西安紫光国芯半导体股份有限公司模拟设计服务团队,旨在为客户提供完整的模拟/混合信号IP所需全流程设计服务,涵盖了从IP设计规格(SPEC)定义,电路设计,全定制版图设计到最终交付代工厂生产数据(GDS)的输出,以及后续芯片测试支持;也包括混合信号IP中数字模块的设计(RTL)和验证,行为级模型(Behavior Model)建立以及最终数字后端实现;本团队具有大量丰富经验的模拟集成电路设计师(平均工作年限大于8年)和全定制模拟版图设计师(平均工作年限大于10年)。

服务内容

• 模拟IP的电路设计服务(从SPEC定义到电路设计数据输出)

• 混合信号IP的电路设计服务(从SPEC定义到电路设计数据输出)

• 模拟IP全定制版图设计服务(从电路输入到GDS/LEF输出)

• 混合信号IP中的数字模块RTL设计,验证以及后端的半定制实现

• 模拟IP和混合信号IP的行为级模型建立和验证

• 模拟IP和混合信号IP的芯片测试支持

我们的能力

团队能力

• 模拟电路设计团队拥有大量经验丰富的资深模拟电路和混合信号电路设计师,平均的工作年限大于8年,具有丰富的芯片量产和测试支持经验(涵盖时钟类,电源管理类,高速接口类等多个领域)。

项目经验

• DRAM: > 40 项目流片、量产,负责DRAM PHY 和 Device中电源管理类模块(BGR、Charge Pump、LDO、POR),时钟类模块(OSC、DLL、PLL)和IO类模块(Receiver、OCD、ODT、ESD)等设计、验证和测试支持工作。

• Baseband: > 10 项目流片、量产,负责基带芯片中电源管理类IP(BGR、LDO)和时钟类IP(OSC、PLL: 整数和小数)等设计、验证和测试支持工作。

• CPU: > 5 项目流片、量产,负责低功率内核中模拟IP(Power gate、XTAL、LC-PLL、Ring-PLL、DLLs、低噪声LDO、高速LDO、SD-ADC、Temp Sensor、Clock Divider etc.)的设计、验证和测试支持工作。

• FPGA:> 10 项目流片、量产,负责FPGA中模拟IP(XTAL、PLL、OSCs、BGR、LDOs、LVDS、SAR ADC、RX etc.)的设计、

• 验证和测试支持工作。

• MCU、NFC、Wireless Charger:> 10 项目流片、量产,负责模拟IP(DC-DC、PLL、LDOs、XTAL、OSCs、VDT、TD、CMP、OPA、POR、BGR)的设计、验证和测试支持工作。

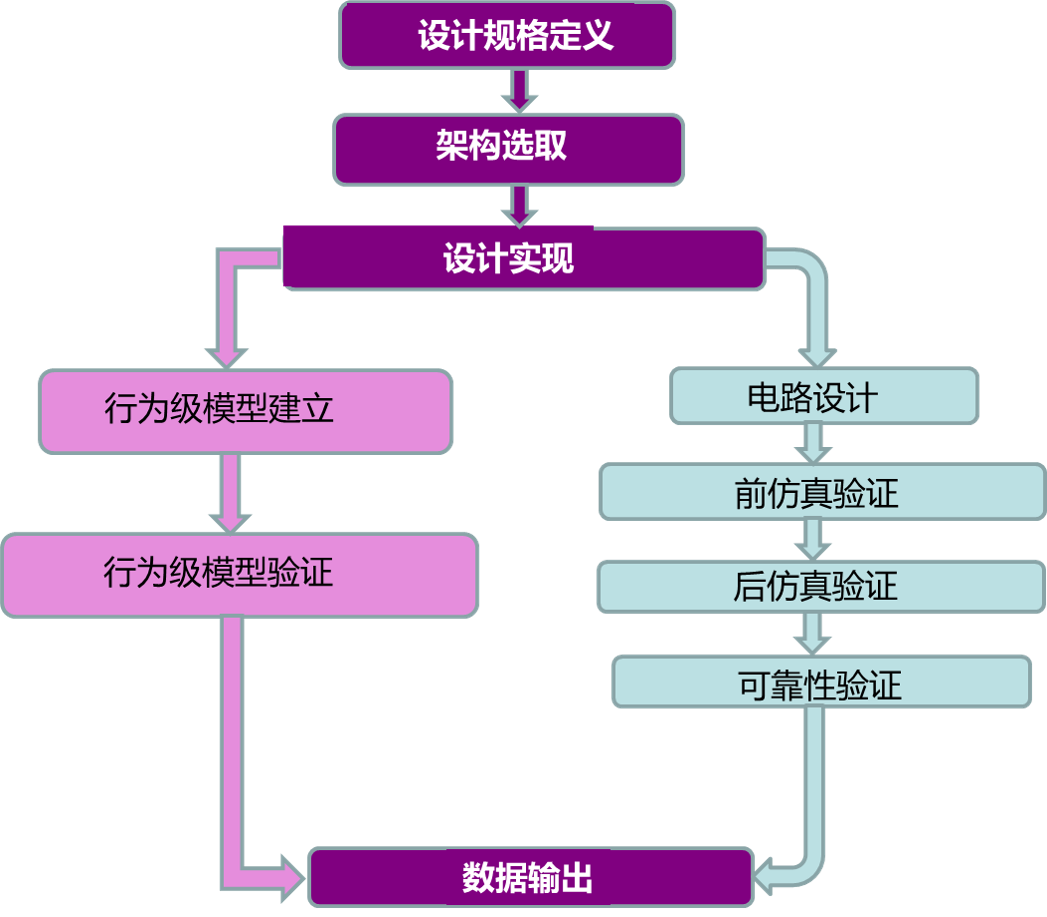

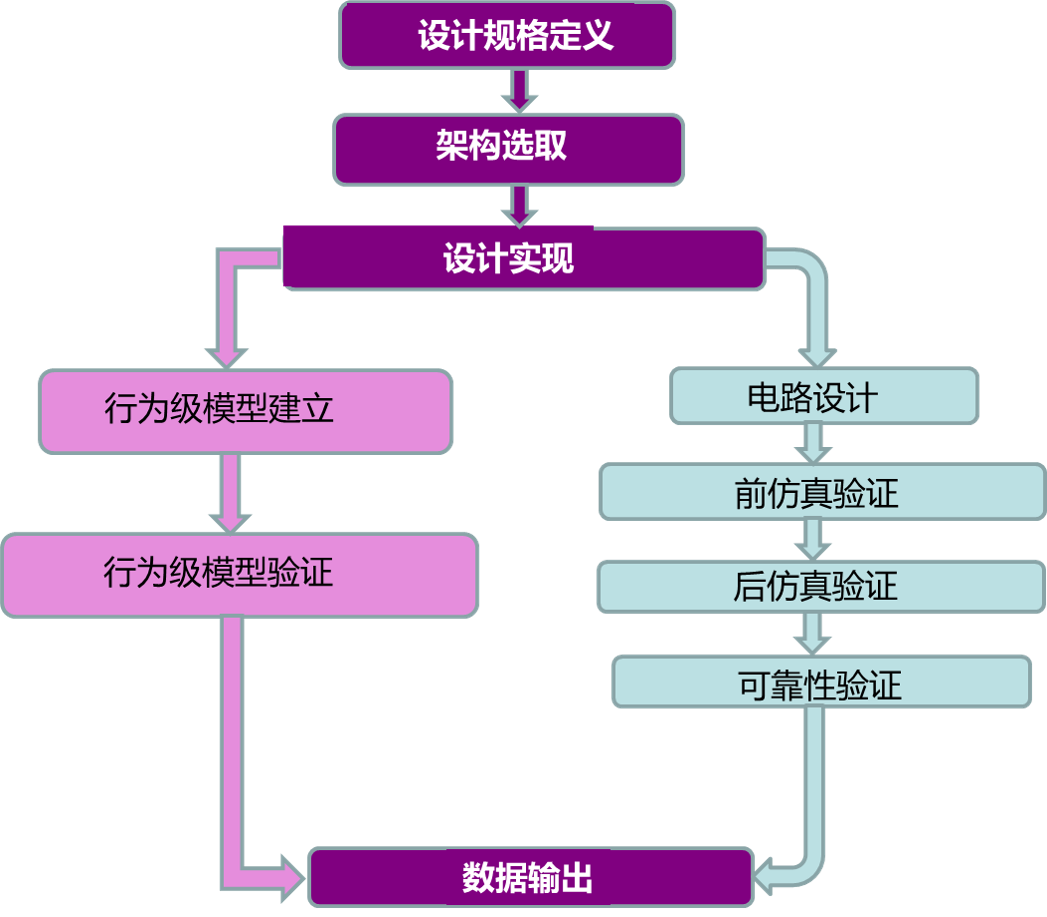

电路设计基本流程

电路设计基本流程