模拟版图设计团队拥有诸多经验非常丰富的专家级设计师,团队平均的工作年限大10年,涉及的工艺节点基本涵盖全工艺范围:从0.18um高压 BCD工艺开始的FinFet工艺,以及诸多节点的Memory定制工艺。拥有丰富的从模块级到芯片级的版图设计经验, 丰富的高速(高速IO接口,高速PLL:Ring PLL和LC PLL)和高精度/高匹配度的版图设计经验。

工艺节点

•DRAM工艺: 65/46/45/38/25nm technology

•逻辑工艺: 180(BCD)/110/65/55/40nm technology

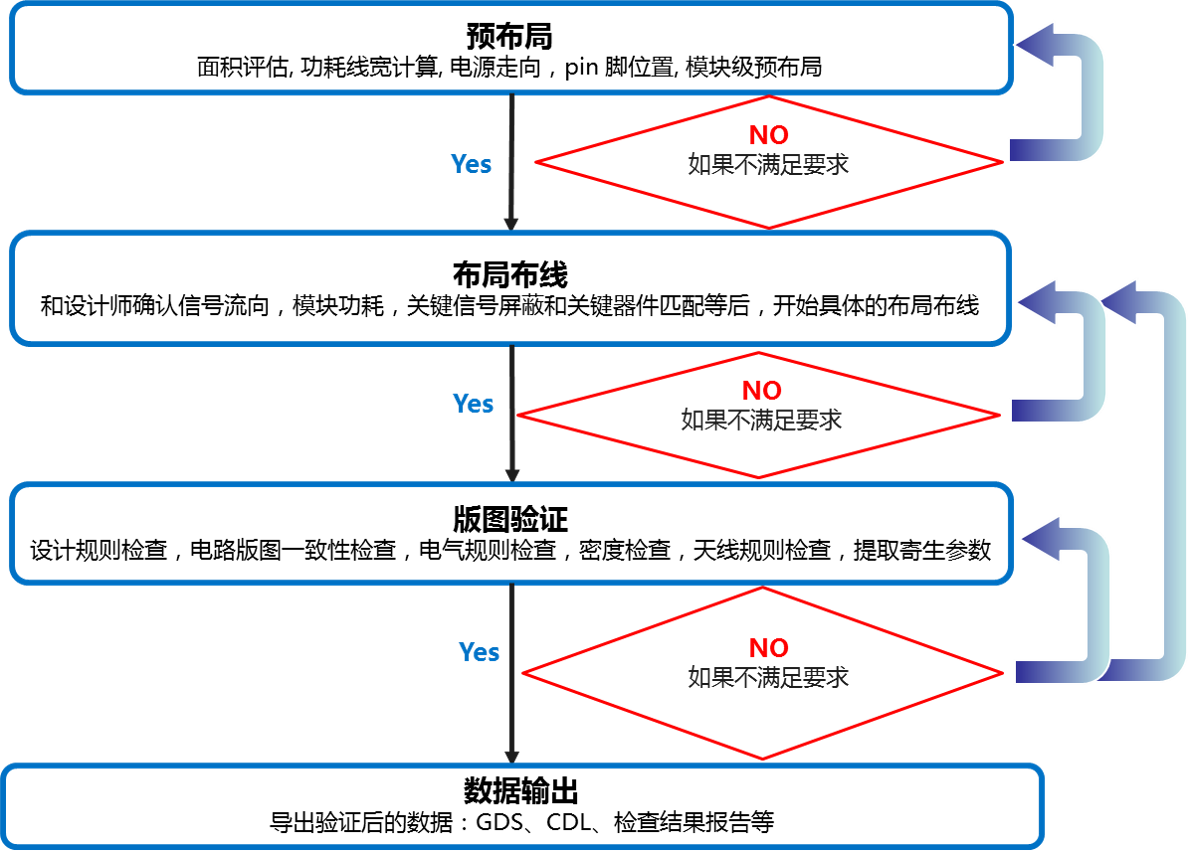

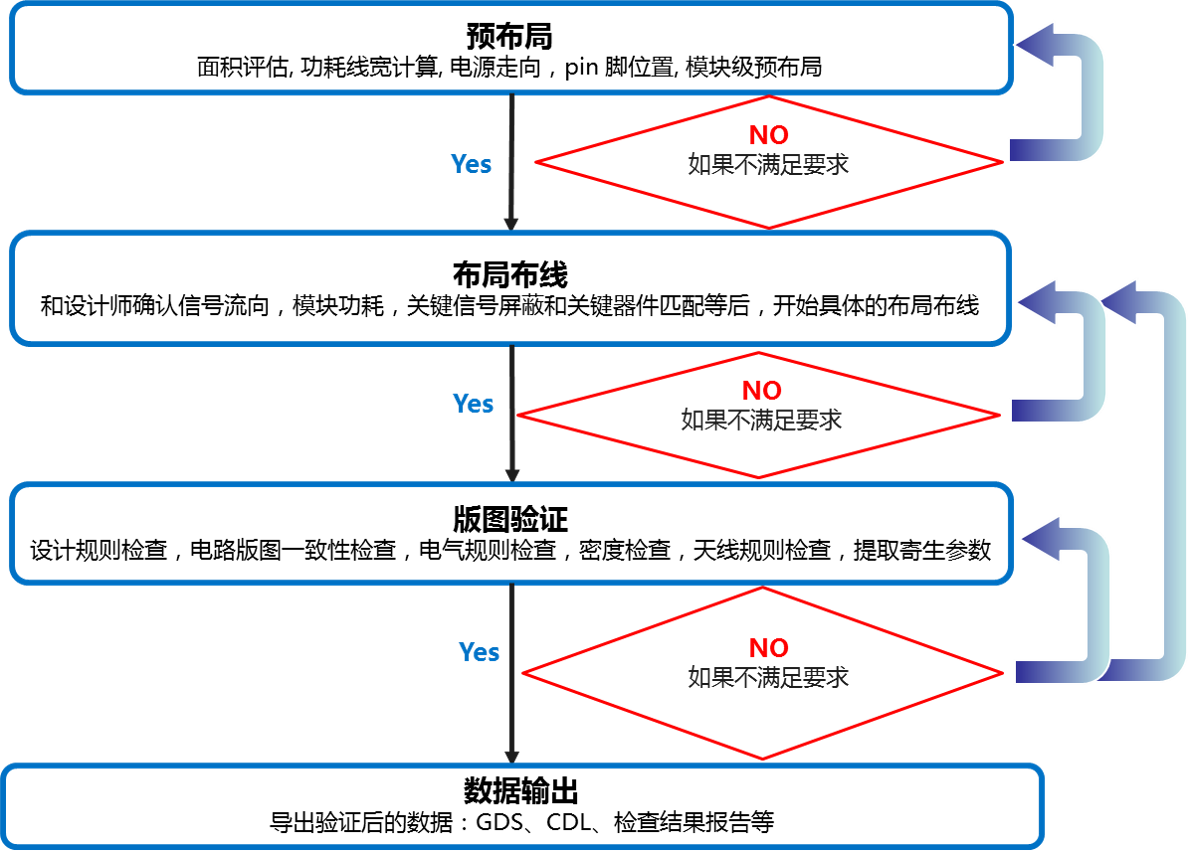

版图设计基本流程

版图设计基本流程

商业模式

商业模式

西安紫光国芯提供灵活的商业合作模式来满足不同客户和客户项目不同阶段的需求

• 电路设计&版图设计服务:客户提出设计规格,西安紫光国芯输出完整的IP数据(CDL/GDS/LEF/Lib etc.)

• 电路设计或版图设计服务:西安紫光国芯可以提供单纯的电路设计或者版图设计服务,输出数据方式与客户协商

GDDR6物理接口 IP

GDDR6存储器物理接口是存储控制器和GDDR6存储器颗粒进行数据通讯交互的桥梁,主要负责将存储控制器端的信号(操作指令、读写地址、数据和时钟等)转换为符合存储器接口协议规范(JEDEC250和DFI 3.1)的时序和电平信号(数据率支持最高16Gbps),并以规范的格式从存储控制器端把信号传送到外部存储器,同时接收外部存储器的数据信号,并将其转换为特定的数据格式传送给存储控制器来完成数据交互。

关键指标

• 已在 Global Foundries 12nm LP FinFet 工艺流片并可提供测试报告

• 兼容JEDEC标准No.250 GDDR6 SDRAMs器件(速率高达16Gbps)

• 内嵌低噪声PLL来满足时序指标

• 内嵌PVT补偿的延迟链

• 支持双通道 GDDR6 存储器颗粒

• 支持回环测试(Loop Back Test)模式

• 支持QDR和DDR模式的数据传输

• 支持每八位一组WCK和每十六位一组WCK模式

• 支持DBI和CABI模式

• 支持接收器(RX) 判决反馈均衡(DFE)校准和可编程的发射器去加重(de-emphasis)

• 支持输出驱动阻抗的自动校准

• 支持PHY的各种训练模式: 命令地址训练(CA), 读写时钟对命令地址时钟训练(WCK2CK), 以及读数据训练和写数据训练(支持单个DQ训练)

• 片上可读出的温度传感器

• 支持DRAM内建自测试模式 (BIST)