近日,西安紫光国芯半导体股份有限公司(以下简称“西安紫光国芯”)在VLSI 2023技术与电路研讨会上(2023 Symposium on VLSI Technology and Circuits)公开发表了技术论文——《基于小间距混合键合和mini-TSV的135 GBps/Gbit 0.66 pJ/bit 嵌入式多层阵列 DRAM》(135 GBps/Gbit 0.66 pJ/bit Stacked Embedded DRAM with Multilayer Arrays by Fine Pitch Hybrid Bonding and Mini-TSV)。该论文的发表,是西安紫光国芯在SeDRAM®方向上持续创新的最新突破。

本年度 VLSI 会议共收到全球投稿 632 篇,在最终录取的212 篇中,仅有2篇来自中国内地企业,其中1篇便是来自西安紫光国芯的嵌入式多层阵列DRAM论文。

论文第一作者西安紫光国芯副总裁王嵩代表公司作论文报告

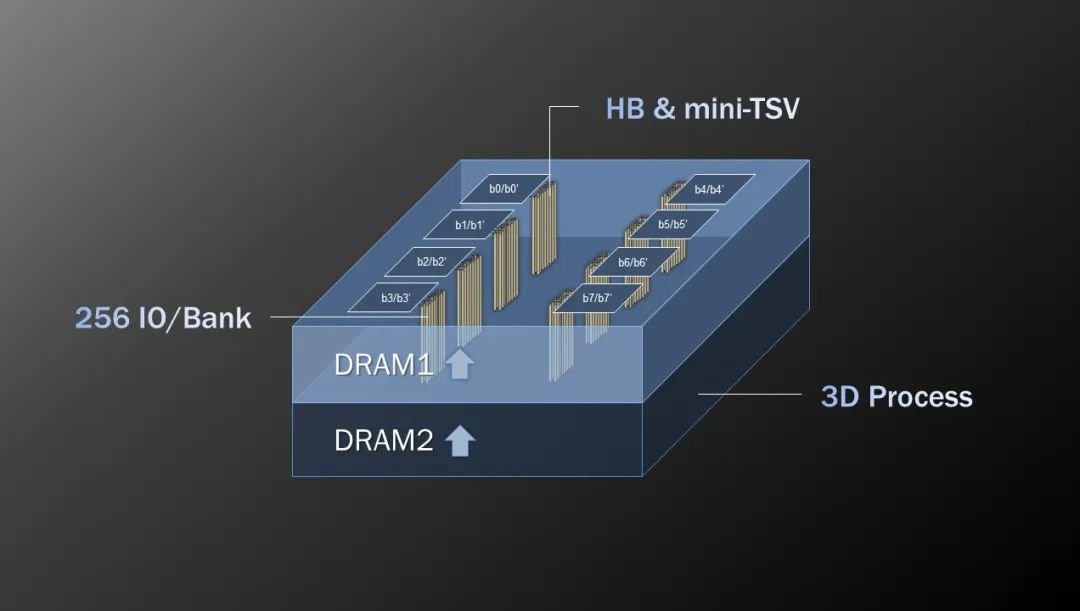

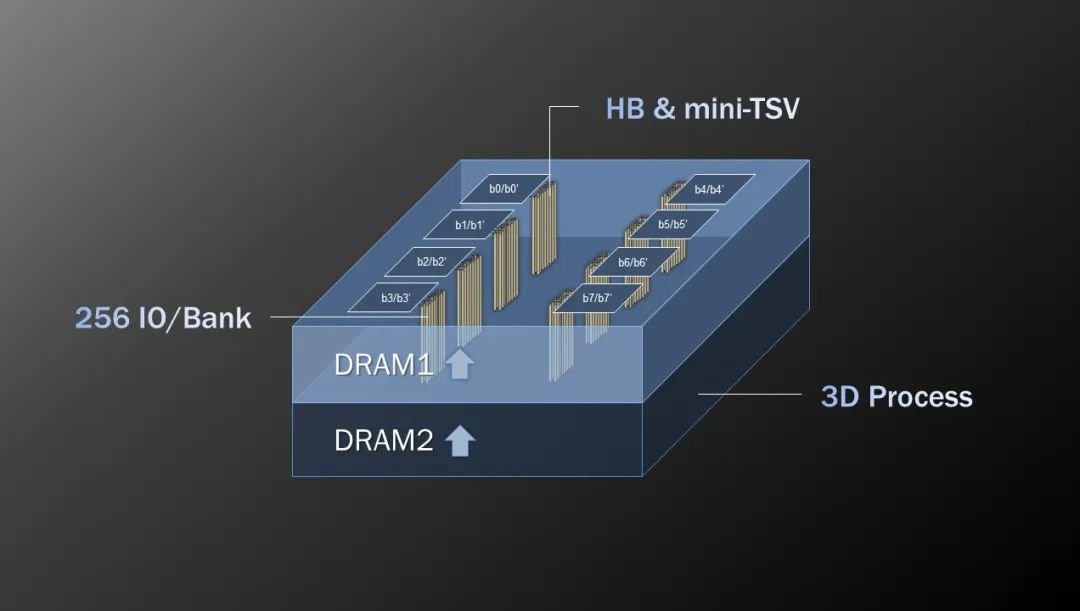

本次VLSI 2023上,西安紫光国芯发布的新一代多层阵列SeDRAM,相较于上一代单层阵列结构,新一代技术平台主要采用了低温混合键合技术(Hybrid Bonding,HB)和mini-TSV堆积技术。该技术平台每Gbit由2048个数据接口组成,每个接口数据速度达541 Mbps,最终实现业界领先的135 GBps/Gbit带宽和0.66 pJ/bit能效,为叠加更多层DRAM阵列结构提供先进有效的解决方案。

嵌入式多层阵列SeDRAM示意图

论文通讯作者西安紫光国芯总经理江喜平表示,“2020年IEDM我们发布了第一代SeDRAM技术,之后我们实现了多款产品的大规模量产。这次发布的新一代多层阵列SeDRAM技术,实现了更小的电容电阻、更大的带宽和容量,可广泛应用于近存计算、大数据处理和高性能计算等领域。”

西安紫光国芯异质集成嵌入式DRAM(SeDRAM)基于混合键合技术实现了逻辑单元和DRAM阵列三维集成,多项研发成果已先后在IEDM 2020、CICC 2021、ISSCC 2022等多个期刊和会议上公开发表和作专题报告。