# SCF2BW1I3A 2Gb 3.3V SPI NAND

# **Data Sheet**

Rev. A

| Revision History |          |                                              |  |  |  |  |  |

|------------------|----------|----------------------------------------------|--|--|--|--|--|

| Date             | Revision | Subjects (major changes since last revision) |  |  |  |  |  |

| 2025-02-19       | A        | Initial Release                              |  |  |  |  |  |

# Contents

| Co | ntents |                                                           | 3  |

|----|--------|-----------------------------------------------------------|----|

| 1. | Produ  | ct list                                                   | 6  |

| 2. | Packa  | iges and Pins                                             | 6  |

|    | 2.1.   | Package Type                                              | 6  |

|    | 2.2.   | Pin Description                                           |    |

| 3. | Block  | Diagram                                                   |    |

| 4. | Memo   | ory Mapping                                               | 7  |

| 5. | Array  | Organization                                              | 8  |

| 6. | Device | e Operations                                              | g  |

|    | 6.1.   | SPI Modes                                                 | ç  |

|    | 6.2.   | SPI Protocols                                             |    |

|    |        | Standard SPI                                              |    |

|    |        | Extended SPI                                              |    |

|    | 6.3.   | Pin Descriptions.                                         |    |

|    | 6.3.1. | CS#                                                       |    |

|    |        | SCK                                                       |    |

|    |        | SI/IO0                                                    |    |

|    |        | SO/IO1                                                    |    |

|    |        | WP#/IO2                                                   |    |

|    |        | HOLD#/IO3                                                 |    |

| 7. |        | nand Definition                                           |    |

|    | 7.1.   | Command Set Tables                                        | 12 |

|    | 7.2.   | Reset Operations                                          | 14 |

|    | 7.2.1. | RESET (FFh)                                               | 14 |

|    | 7.3.   | WRITE Operations                                          |    |

|    | 7.3.1. | WRITE ENABLE (06h)                                        |    |

|    | 7.3.2. | WRITE DISABLE (04h)                                       |    |

|    | 7.4.   | Feature Operations                                        |    |

|    | 7.4.1. | GET FEATURE (0Fh) and SET FEATURE (1Fh)                   | 16 |

|    | 7.4.2. | Block Lock Register                                       | 17 |

|    | 7.4.3. | Configuration Register Bits                               | 18 |

|    | 7.4.4. | Status Register                                           | 19 |

|    | 7.4.5. | Drive Strength (DRS1, DRS0)                               | 19 |

|    | 7.5.   | READ Operations                                           | 20 |

|    | 7.5.1. | PAGE READ (13h)                                           | 20 |

|    |        | READ FROM CACHE x1 (03h or 0Bh)                           |    |

|    | 7.5.3. | READ FROM CACHE x2 (3Bh)                                  | 22 |

|    | 7.5.4. | READ FROM CACHE x4 (6Bh)                                  | 23 |

|    | 7.5.5. | READ ID (9Fh)                                             | 24 |

|    | 7.5.6. | Parameter Page                                            | 25 |

|    | 7.5.7. | UniqueID Page                                             | 27 |

|    | 7.6.   | Program Operations                                        | 27 |

|    | 7.6.1. | PAGE PROGRAM                                              | 27 |

|    | 7.6.2. | RANDOM DATA PROGRAM                                       | 30 |

|    | 7.6.3. | PROGRAM LOAD x4 (32h) / PROGRAM LOAD RANDOM DATA x4 (34h) | 31 |

|    | 7.6.4. | INTERNAL DATA MOVE                                        | 32 |

|    | 7.7.   | BLOCK ERASE (D8h)                                         | 32 |

|    | 7.8.   | Block Lock Feature                                        | 34 |

|    | 7.8.1. | Block Lock                                                | 36 |

|    |        | LOCK TIGHT                                                |    |

|    | 7.8.3. | PROTECT Command (PERMANENT BLOCK LOCK PROTECTION 2Ch)     | 37 |

|    | 7.9.   | OTP Feature                                               | 39 |

|    | 7.9.1. | OTP Access Configuration                                  | 39 |

| 7.9.3. OTP DATA PROTECT       4°         7.9.4. OTP Configuration to Disable Protection Command       4°         7.10. Status Register       42         7.11. Error Management       43         7.12. ECC Protection       45         8. Electrical Characteristics       47         8.1. Maximum Rating       47         8.2. Power Up / Power Down       47         8.2.1. SPI Power Up       47         8.2.2. SPI Power Down       48         8.3. DC and AC parameters       48         9. Package diagram       50 |    |         | OTP Area Access                                 |    |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|---------|-------------------------------------------------|----|

| 7.10. Status Register       42         7.11. Error Management       43         7.12. ECC Protection       45         8. Electrical Characteristics       47         8.1. Maximum Rating       47         8.2. Power Up / Power Down       47         8.2.1. SPI Power Up       47         8.2.2. SPI Power Down       48         8.3. DC and AC parameters       48                                                                                                                                                      |    | 7.9.3.  | OTP DATA PROTECT                                | 41 |

| 7.10. Status Register       42         7.11. Error Management       43         7.12. ECC Protection       45         8. Electrical Characteristics       47         8.1. Maximum Rating       47         8.2. Power Up / Power Down       47         8.2.1. SPI Power Up       47         8.2.2. SPI Power Down       48         8.3. DC and AC parameters       48                                                                                                                                                      |    | 7.9.4.  | OTP Configuration to Disable Protection Command | 41 |

| 7.11. Error Management                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |    |         |                                                 |    |

| 8. Electrical Characteristics       47         8.1. Maximum Rating       47         8.2. Power Up / Power Down       47         8.2.1. SPI Power Up       47         8.2.2. SPI Power Down       48         8.3. DC and AC parameters       48                                                                                                                                                                                                                                                                           |    | 7.11.   | Error Management                                | 43 |

| 8.1. Maximum Rating                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |    | 7.12.   | ECC Protection                                  | 45 |

| 8.2. Power Up / Power Down       47         8.2.1. SPI Power Up       47         8.2.2. SPI Power Down       48         8.3. DC and AC parameters       48                                                                                                                                                                                                                                                                                                                                                               | 8. | Electri | cal Characteristics                             | 47 |

| 8.2.1. SPI Power Up       47         8.2.2. SPI Power Down       48         8.3. DC and AC parameters       48                                                                                                                                                                                                                                                                                                                                                                                                           |    | 8.1.    | Maximum Rating                                  | 47 |

| 8.2.2. SPI Power Down       48         8.3. DC and AC parameters       48                                                                                                                                                                                                                                                                                                                                                                                                                                                |    | 8.2.    | Power Up / Power Down                           | 47 |

| 8.2.2. SPI Power Down       48         8.3. DC and AC parameters       48                                                                                                                                                                                                                                                                                                                                                                                                                                                |    | 8.2.1.  | SPI Power Up                                    | 47 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |    | 8.2.2.  | SPI Power Down                                  | 48 |

| 9. Package diagram53                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |    | 8.3.    | DC and AC parameters                            | 48 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 9. | Packa   | ge diagram                                      | 53 |

#### **Features**

#### Single-level cell (SLC) technology

#### Organization

- Page size: 2176 bytes (2048 + 128)

Block size: 64 pages

- Plane size: 1 plane with 1024 blocks

Device size: 2Gb with 2048 blocks

#### Serial Protocol Interface

SPI clock polarity and phase Mode 0 and Mode 3

Standard SPI: SCK, CS#, SI, SO, WP#,

Hold#

Dual SPI: SCK, CS#, SIO0, SIO1,

WP#,Hold#

Quad SPI: SCK, CS#, SIO0, SIO1, SIO2, SIO3

#### Key Parameters

- Operation voltage

· VCC: 2.7 To 3.6V

- Operation temperature

· Commercial: -20° C to +70° C

· Industry: -40° C to +85° C

Clock frequency

· 133MHz @3.3V (max)

- Array Performance

· Page Read: 25us (max) with on-die ECC disabled; 95us (max) with on- die ECC enabled

· Page Program: 270us (typ) with on-die ECC disabled; 320us (typ) with on-die ECC enabled

· Block Erase: 2ms (typ)

The internal ECC is designed as 8-bit/544bytes at least; when the internal ECC is disabled, the external 8-bit ECC is needed.

#### Advanced Command Set

- Read from Cache x2 (3Bh)

- Read from Cache x4 (6Bh)

- Program Load x4 (32h) / Program Load

Random Data x4 (34h)

- Permanent Block Lock Protection (2Ch)

#### Device Initialization

Automatic device initialization with the First Page Data Auto Load on Power Up with ECC on always. To use this optional feature, user needs to write the first page with on-die ECC enabled.

#### Security

- Blocks 0-3 are valid when shipped from factory with ECC

- Software Write Protection with Block Lock Register

- Hardware Write Protection with WP# to freeze

Block Protect (BP) bits

- Lock Tight to freeze BP bits during one power cycle instead of WP#

- Permanent Block Lock Protection

OTP Space

- · 10 pages one-time programmable NAND Flash memory area

#### Quality and Reliability

Data Retention: 10 years

- 100,000 P/E cycles for Industry

#### Package

WSON8 (8mm x 6mm)

## Product list

List shows all possible products within the 2Gb 3.3V NAND component generation.

List 1 - Ordering Information for 2Gb 3.3V SPI NAND Components

| Product Type                                 | ECC   | Endurance | speed  | voltage | Package   | Note |  |  |  |

|----------------------------------------------|-------|-----------|--------|---------|-----------|------|--|--|--|

| Industrial Temperature Range (-40°C to 85°C) |       |           |        |         |           |      |  |  |  |

| SCF2BW1I3A                                   | 8bits | 100K      | 133Mhz | 3.3V    | WSON8 6*8 |      |  |  |  |

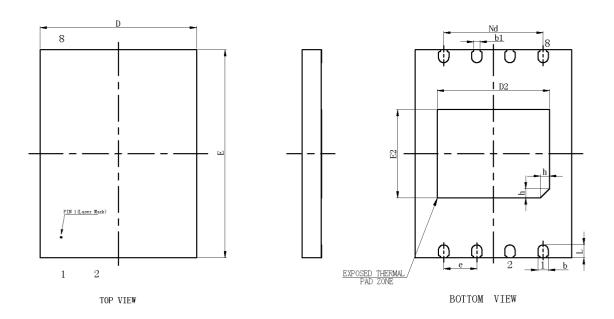

# 2. Packages and Pins

## 2.1. Package Type

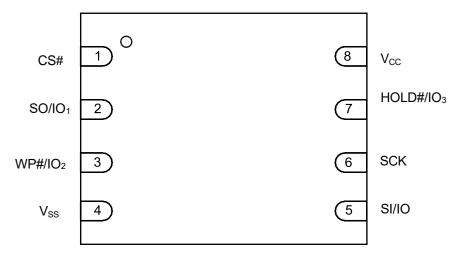

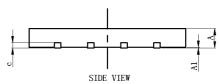

SCF2BW1I3A is offered in WSON8 packages as shown in Figure 1. Package diagrams and dimensions are illustrated at the end of this datasheet.

Figure 1: Pin Assignments of WSON8

## 2.2. Pin Description

**Table 1: Pin Description**

| Symbol    | Туре   | Name and function                                                                                                            |

|-----------|--------|------------------------------------------------------------------------------------------------------------------------------|

| CS#       | Input  | Chip Select: The device selection control.                                                                                   |

| SCK       | Input  | Serial Clock: The serial clock input.                                                                                        |

| SI/IO0    | I/O    | <b>Serial Data Input</b> or <b>Serial Data Input &amp; Output</b> (for X2/X4 IO): Transfer data serially into the device.    |

| SO/IO1    | I/O    | <b>Serial Data Output</b> or <b>Serial Data Input &amp; Output</b> (for X2/X4 IO): Transfer data serially out of the device. |

| WP#/IO2   | I/O    | Write Protect or Serial Data Input & Output (for X4 IO): Prevent the block lock bits from being overwritten.                 |

| HOLD#/IO3 | I/O    | Hold or Serial Data Input & Output (for X4 IO): Pause any serial communication with the device without de-selecting it.      |

| VCC       | Supply | Vcc: The power supply for device.                                                                                            |

| Vss       | Supply | Vss: Ground.                                                                                                                 |

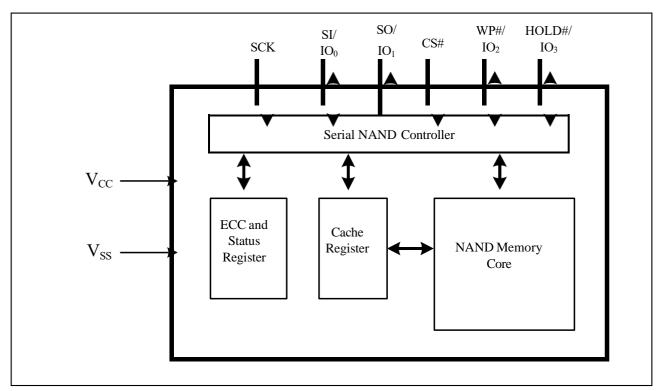

# 3. Block Diagram

Figure 2: SPI NAND Flash Memory Block Diagram

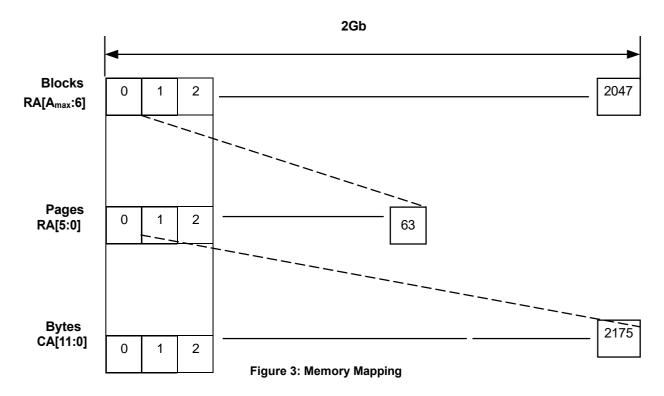

# 4. Memory Mapping

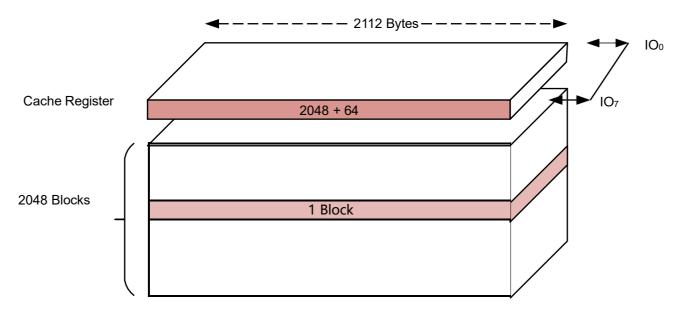

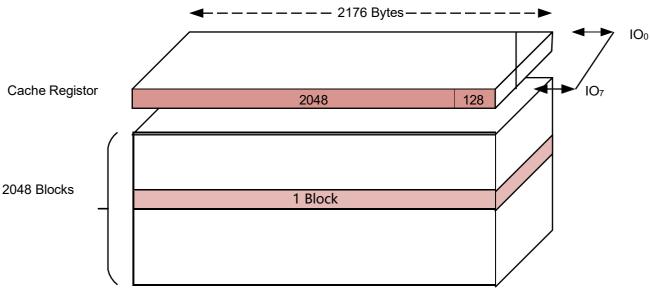

# 5. Array Organization

## **Array Organization:**

• Page size: 2176 bytes (2048 + 128)

Block size: 64 pages

Plane size: 1 plane with 2048 blocksDevice size: 2Gb with 2048 blocks

Figure 4: Array Organization (ECC ON)

Figure 5: Array Organization (ECC OFF)

## 6. Device Operations

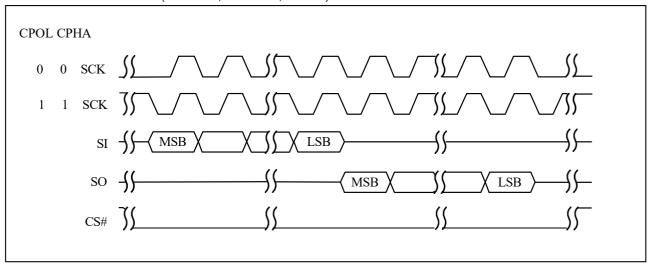

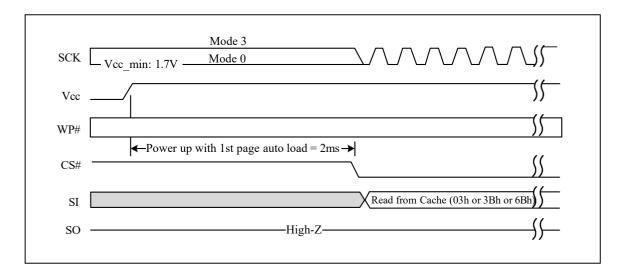

#### 6.1. SPI Modes

SPI NAND supports two SPI modes:

- CPOL = 0, CPHA = 0 (Mode 0)

- CPOL = 1, CPHA = 1 (Mode 3)

Input data is latched in on the rising edge of SCK, and output data is available from the falling edge of SCK for both modes.

When the bus master is in standby mode:

- SCK remains at 0 for (CPOL = 0, CPHA = 0, Mode 0)

- SCK remains at 1 for (CPOL = 1, CPHA = 1, Mode 3)

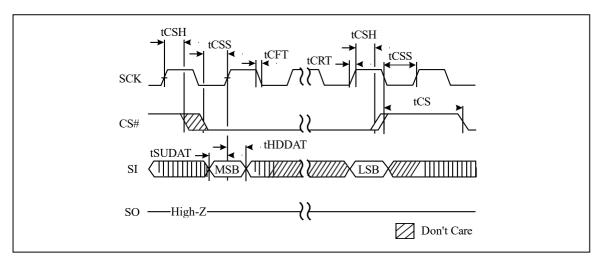

Figure 6: SPI Modes Timing

All timing diagrams shown in this datasheet are Mode 0.

#### 6.2. SPI Protocols

The device supports two serial protocols:

- Standard SPI protocol

- Extended SPI protocol

Using different Command Op Codes can configure the device to one of these protocols.

#### 6.2.1. Standard SPI

Instruction, addresses and data are transmitted on a single data line at standard SPI protocol. Instruction, address and Input data is latched in on the rising edge of SCK through SI; Output data is available from the falling edge of SCK through SO.

#### 6.2.2. Extended SPI

An extension of the standard SPI protocol. Instructions and address are transmitted on a signal data line through SI, while data are transmitted by two or four data lines depending on the instruction.

## 6.3. Pin Descriptions

#### 6.3.1. CS#

Chip select (CS#) activates or deactivates the device. When CS# goes LOW, the device is placed in active mode. When CS# is HIGH, the device is placed in inactive mode and IO is High-Z.

#### 6.3.2. SCK

Serial clock (SCK) provides interface timing for SPI NAND. Commands, addresses, and data are latched on the rising edge of SCK. Data is placed on IO at the falling edge of SCK. When CS# is HIGH, SCK must return either HIGH or LOW.

#### 6.3.3. SI/IO0

Writes use serial data in (SI). Commands, addresses, and data are transferred on SI in x1 mode at the rising edge of SCK. SI must not be driven by the host during x2 or x4 read operations.

IO<sub>0</sub> operation is enabled by issuing a READ FROM CACHE x2 or x4 command with data being clocked out of the device at the falling edge of SCK or by issuing a PROGRAM LOAD x4 or PROGRAM LOAD RANDOM DATA x4 with data being clocked into the device at the rising edge of SCK. During this time the host must wait until the READ FROM CACHE x2 or x4 command is complete before driving IO<sub>0</sub>.

#### 6.3.4. SO/IO1

Reads use serial data out (SO). Device reads are performed in x1, or x2, or x4 modes. SO acts as the only output in x1 READ operations, and as IO1 in x2, x4 read operations or x4 write operation.

Data is clocked out of the device on SO/IO1 at the falling edge of SCK control signals. When writing to the device in x4 mode, data is clocked into the device on SO/IO1 at the rising edge of SCK control signals.

#### 6.3.5. WP#/IO2

Write protect (WP#) prevents the block lock bits (BP0, BP1, BP2, INV and CMP) from being overwritten. If the BRWD bit is set to 1 and WP# is LOW, the block protect bits cannot be altered. WP# must not be driven by the host during READ FROM CACHE x4 operations.

IO2 operation is enabled by issuing a READ FROM CACHE x4 command with data being clocked out of the device at the falling edge of SCK or by issuing a PROGRAM LOAD x4 or PROGRAM LOAD RANDOM DATA x4 with data being clocked into the device at the rising edge of SCK. During this time, the host must wait until the READ FROM CACHE x4 command is completed before driving WP#.

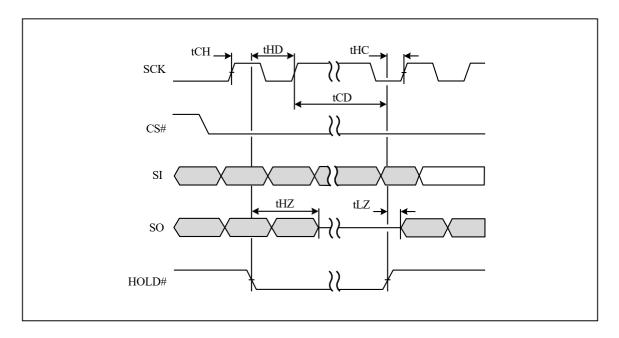

#### 6.3.6. HOLD#/IO3

HOLD# input provides a method to pause serial communication with the device but does not terminate any ERASE, READ, or WRITE operation currently in progress.

Hold mode starts at the falling edge of HOLD# provided SCK is also LOW. If SCK is HIGH when HOLD# goes LOW, hold mode begins after the next falling edge of SCK. Similarly, hold mode is exited at the rising edge of HOLD# provided SCK is also LOW. If SCK is HIGH, hold mode ends after the next falling edge of SCK.

During hold mode, SO is High-Z, and SI and SCK inputs are ignored.

IO3 operation is enabled by issuing a READ FROM CACHE x4 command with data being clocked out of the device at the falling edge of SCK or by issuing a PROGRAM LOAD x4 or PROGRAM LOAD RANDOM DATA x4 with data being clocked into the device at the rising edge of SCK. During this time, the host must wait until the READ FROM CACHE x4 command is completed before driving HOLD#.

## 7. Command Definition

#### 7.1. Command Set Tables

**Table 2: SPI NAND Command Set**

| Commands                              | Op Code  | Address | Dummy | Data                 | Comments                                                                                                            |

|---------------------------------------|----------|---------|-------|----------------------|---------------------------------------------------------------------------------------------------------------------|

|                                       | •        | Bytes   | Bytes | Bytes                |                                                                                                                     |

| RESET                                 | FFh      | 0       | 0     | 0                    | Reset the device                                                                                                    |

| GET FEATURE                           | 0Fh      | 1       | 0     | 1                    | Get Features                                                                                                        |

| SET FEATURE                           | 1Fh      | 1       | 0     | 1                    | Set Features                                                                                                        |

| PAGE READ                             | 13h      | 3       | 0     | 0                    | Array Read                                                                                                          |

| READ FROM CACHE                       | 03h, 0Bh | 2       | 1     | 1 to 2176<br>Or 2112 | Output Cache data at Column address                                                                                 |

| READ FROM CACHE x2                    | 3Bh      | 2       | 1     | 1 to 2176<br>Or 2112 | Output Cache data on IO <sub>0</sub> and IO <sub>1</sub>                                                            |

| READ FROM CACHE x4                    | 6Bh      | 2       | 1     | 1 to 2176            | Output Cache data on IO <sub>0</sub> , IO <sub>1</sub> , IO <sub>2</sub> and                                        |

|                                       |          |         |       | Or 2112              | IO <sub>3</sub>                                                                                                     |

| BLOCK ERASE                           | D8h      | 3       | 0     | 0                    | Block Erase                                                                                                         |

| PROGRAM EXECUTE                       | 10h      | 3       | 0     | 0                    | Array Program                                                                                                       |

| PROGRAM LOAD                          | 02h      | 2       | 0     | 1 to 2176<br>Or 2112 | Load Program data into Cache register                                                                               |

| Program LOAD RANDOM DATA              | 84h      | 2       | 0     | 1 to 2176<br>Or 2112 | Overwrite cache register with input data                                                                            |

| PROGRAM LOAD x4                       | 32h      | 2       | 0     | 1 to 2176            | Load program data into cache register                                                                               |

|                                       |          |         |       | Or 2112              | on IO <sub>0</sub> , IO <sub>1</sub> , IO <sub>2</sub> and IO <sub>3</sub>                                          |

| PROGRAM LOAD<br>RANDOM DATA x4        | 34h      | 2       | 0     | 1 to 2176<br>Or 2112 | Overwrite cache register with input data on IO <sub>0</sub> , IO <sub>1</sub> , IO <sub>2</sub> and IO <sub>3</sub> |

| READ ID                               | 9Fh      | 0       | 1     | 2                    | Read Device ID                                                                                                      |

| WRITE DISABLE                         | 04h      | 0       | 0     | 0                    | Set the WEL bit to 0                                                                                                |

| WRITE ENABLE                          | 06h      | 0       | 0     | 0                    | Set the WEL bit to 1                                                                                                |

| PERMANENT<br>BLOCK LOCK<br>PROTECTION | 2Ch      | 3       | 0     | 0                    | Provide nonvolatile and irreversible protection to boot blocks in groups.                                           |

#### Note:

1. Depending on on-die ECC off or on; when ECC off, byte 0 to 2175 are valid for user access; when ECC on, bytes 0 to 2111 are valid for user access.

In this product, every instruction sequence starts with one-byte instruction code. Depending on the instruction, the instruction sequence involves shifting in address bytes and/or data bytes. Some instructions do not have any address or data bytes.

In the case of Read (Get Feature, all types of read from cache, Read ID) instructions, the shifted-in instruction sequence is followed by a data-out sequence. Chip Select (CS#) can be driven high at any time during the data-out sequence.

In the case of write instructions (Block Erase, Program Execute, all types of Program Load, Write Enable, Write Disable, Permanent block Lock Protection, Set Feature), Page Read (13h) and Reset instructions, the Chip Select (CS#) must be driven high after whole instruction sequence is completed. Otherwise the instruction is not executed and the state of

WEL remains unchanged if these instructions that alter the array or device configuration require Write Enable Latch (WEL) bit to be set.

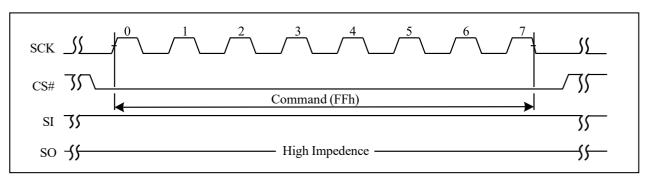

## 7.2. Reset Operations

## 7.2.1. RESET (FFh)

The RESET command is used to put the memory device into a known condition and to abort the command sequence in progress.

Read, Program and Erase commands can be aborted while the device is in the busy state. The contents of the memory location being programmed or the block being erased are no longer valid. The data may be partially erased or programmed, and is invalid. The status register is cleared.

In SPI NAND protocol, RESET command also reset OTP\_CFG2,1,0 (One Time Programmable Configuration Register Bits) back to normal operation. While all the other configuration register bits would not be reset by RESET command to keep the device configuration.

Once the RESET command is issued to the device, the device will take tRST to reset. During this period, no other command could be accepted except Get Feature command.

Figure 7: RESET (FFh) Timing

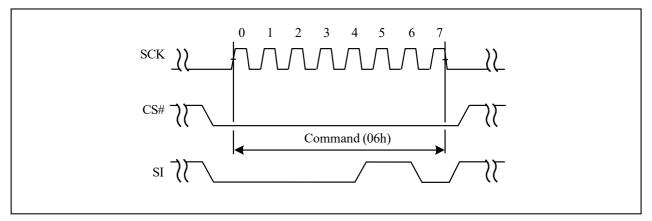

## 7.3. WRITE Operations

## 7.3.1. WRITE ENABLE (06h)

The WRITE ENABLE (06h) command sets the WEL bit in the status register to 1. WRITE ENABLE is required in the following operations that change the contents of the memory array:

- Page Program

- OTP Program

- Block Erase

- Permanent Block Lock Protection

Figure 8: WRITE ENABLE (06h) Timing

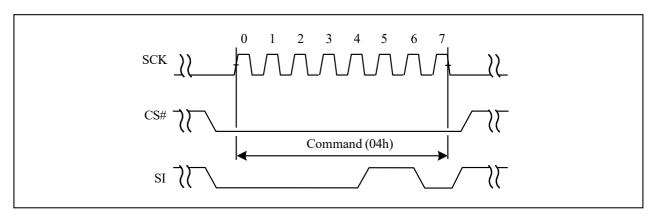

## 7.3.2. WRITE DISABLE (04h)

The WRITE DISABLE (04h) command clears the WEL bit in the status register to 0. This disables the following operations:

- Page Program

- OTP Program

- Block Erase

- Permanent Block Lock Protection

Figure 9: WRITE DISABLE (04h) Timing

### 7.4. Feature Operations

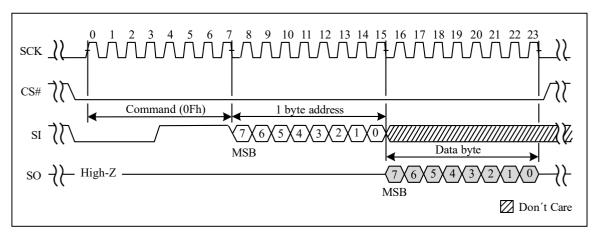

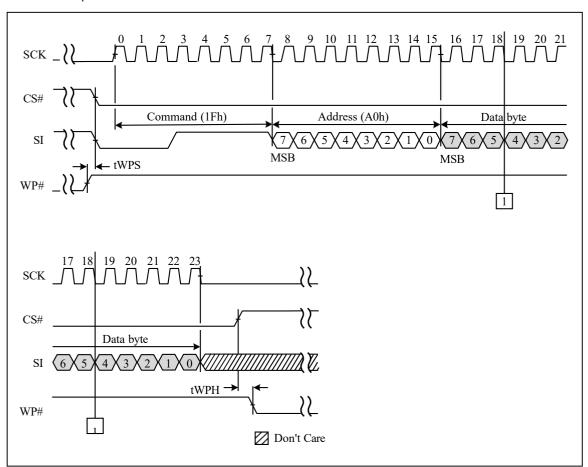

## 7.4.1. GET FEATURE (0Fh) and SET FEATURE (1Fh)

The GET FEATURE (0Fh) and SET FEATURE (1Fh) commands are used to alter the device behavior from the default power-on behavior. These commands use a 1-byte feature address to determine which feature is to be read or modified. Features such as OTP and block locking can be enabled or disabled by setting specific bits in feature address A0h and B0h. The status register is mostly read, except WEL, which is a writable bit with the WRITE ENABLE (06h) command.

When a feature is set, it remains active until the device is power cycled or the feature is written to by SET FEATURE command. Unless otherwise specified in the following table, once the device is set, it remains set, even if a RESET (FFh) command is issued.

**Note:** SET FEATURE command only could be executed during device ready state (OIP = 0); otherwise this command would be ignored.

| Register       | Address | Data Bits         |          |                |                |          |          |          |          |  |

|----------------|---------|-------------------|----------|----------------|----------------|----------|----------|----------|----------|--|

| 3              |         | 7                 | 6        | 5              | 4              | 3        | 2        | 1        | 0        |  |

| Block Lock     | A0h     | BRWD <sup>1</sup> | Reserved | BP2            | BP1            | BP0      | INV      | CMP      | Reserved |  |

| Configuration  | B0h     | OTP               | OTP      | LOT_<br>Enable | ECC_<br>Enable | Reserved | Reserved | OTP      | QE       |  |

|                |         | CFG<br>2          | CFG<br>1 |                |                |          |          | CFG<br>0 |          |  |

| Status         | C0h     | Reserved          | ECCS2    | ECCS1          | ECCS0          | P_FAIL   | E_FAIL   | WEL      | OIP      |  |

| Drive strength | D0h     | Reserved          | DRS1     | DRS0           | Reserved       | Reserved | Reserved | Reserved | Reserved |  |

**Table 3: Feature Settings**

#### Note:

1.lf BRWD (block lock register write disabled) is enabled and WP# is LOW, then bits 7, 5, 4, 3, 2 and 1 at the Block Lock register cannot be changed

Figure 10: GET FEATURE (0Fh) Timing

Figure 11: SET FEATURE (1Fh) Timing

## 7.4.2. Block Lock Register

This register contains volatile block protection bits and BRWD bit. The default value of this register is 3Eh after power up.

| Bit | Name     | Attribute | Description                                                              |

|-----|----------|-----------|--------------------------------------------------------------------------|

| 7   | BRWD     | R/W       | Default = 0; when BRWD = 1, enable hardware protection mode with WP# low |

| 6   | Reserved | Read Only | Default = 0                                                              |

| 5   | BP2      | R/W       |                                                                          |

| 4   | BP1      | R/W       | Default = 111XX to protect entire array                                  |

| 3   | BP0      | R/W       |                                                                          |

| 2   | INV      | R/W       |                                                                          |

| 1   | CMP      | R/W       |                                                                          |

| 0   | Reserved | Read Only | Default = 0                                                              |

**Table 4: Block Lock Register**

#### 7.4.2.1. Volatile Block Protection

The volatile Block Protect bits (BP bits) (BP2, BP1, BP0), Invert bit (INV) and Complementary bit (CMP) in block lock register allow part of the memory or the entire array to be configured as read-only. The default value for the BP bits, INV and CMP bit are 1 after power up to protect the entire array.

The BP bits cannot be changed by SET FEATURE command when the BRWD bit is set to '1' and the WP# pin is driven low (Hardware protected mode). Noted when QE is set to '1', this hardware protected mode will be disabled.

## 7.4.2.2. BRWD bit (Block Lock Register Write Disable)

The BRWD bit is operated in conjunction with the Write protect (WP#) signal. The BRWD bit and WP# signal allow the device to be in the hardware protected mode (BRWD = 1 and WP# is low). In this mode, BP bits become read-only. The default value for BRWD bit is 0 after power up.

When QE is set to '1', hardware protected mode is disabled.

### 7.4.3. Configuration Register Bits

**Table 5: Configuration Register Bits**

| Bit | Name       | Attribute | Description                                                                                                        |

|-----|------------|-----------|--------------------------------------------------------------------------------------------------------------------|

| 7   | OTP_CFG2   | R/W       | Default = '000' to enable normal operation '010' to enable OTP access                                              |

| 6   | OTP_CFG1   | R/W       | '110' to enable OTP data protection bit access '111' to enable Boot block lock protection configuration bit access |

| 1   | OTP_CFG0   | R/W       | others to enable normal operation                                                                                  |

| 5   | LOT_Enable | R/W       | Default = 0 not to protect BP bits from changes                                                                    |

| 4   | ECC_Enable | R/W       | Default = 1 to indicate ECC on/off after device initialization                                                     |

| 3   | Reserved   | Read Only | Default = 0                                                                                                        |

| 2   | Reserved   | Read Only | Default = 0                                                                                                        |

| 0   | QE         | R/W       | Quad mode enable/disable bit; Default = 0 indicates Quad mode is disabled                                          |

# 7.4.3.1. OTP (One Time Programmable) Configuration Register Bits (OTP CFG2,1,0)

In addition to the main memory array, a 10 pages OTP area of 2112-byte each is provided for the system to store critical data that cannot be changed once OTP DATA protection bit is set to '0'.

To protect boot block lock protection from further change, this product also provides a nonvolatile configuration to disable boot block lock protection for the user. This is also implemented through Program Execute by reserving one page of flash array to store this configuration bit.

OTP\_CFG2,1,0 controls the access entry to above different operations. The default value after power up or a RESET command is 0.

## 7.4.3.2. Lock Tight Enable (LOT\_ENABLE)

LOT\_Enable bit provides a software protection to protect BP bits, INV and CMP bit when hardware protection mode is disabled for Quad operations.

Note that once this bit is set to '1', only power-down and power-up cycle could change this bit to '0' state.

## 7.4.3.3. ECC Enable (ECC\_ENABLE)

This product has an on-die ECC algorithm that can be used to obtain the data integrity. Internal ECC calculation is done during page programming, and the result is stored in reserved ECC area for each page. During the array read operation, ECC engine will verify the data values according to stored ECC information and to make necessary corrections if needed. Correction status is indicated by the ECC status bits.

ECC\_Enable = 1 indicates on-die ECC turned-on; conversely, ECC\_Enable = 0 indicated on- die ECC turned-off.

ECC\_Enable will be as "1" indicates on-die ECC turned on after device initialization. This bit could be changed by SET FEATURE command at feature address B0h; while RESET command could not change this bit to default value.

## 7.4.3.4. QE (Quad mode Enable bit)

QE bit is designed to support x4 mode and enable x4 mode commands. During x4 mode, WP#/HOLD# is used as IO2/IO3 respectively. The user might not drive these two pins during command or address cycles; this might cause some accidental hardware protection mode enabled or accidental HOLD condition entries in applications. This bit could be used to disable hardware protection mode and HOLD condition as well as enable x4 command acceptance.

## 7.4.4. Status Register

Status register bits shows the dice status; all bits are read-only register except WEL which

could be changed by WRITE DISABLE (04h) and WRITE ENABE (06h) commands. None of bits could be changed by SET FEATURE (1Fh) command.

## 7.4.5. Drive Strength (DRS1, DRS0)

Output Drive Strength bits can be used to adjust output pin strength. Default Drive Strength bits (DRS1, DRS0) is (1, 0) which means default Drive Strength is 50%.

**Table 6: Drive Strength Bits**

| 3    |      |                |  |  |  |  |  |  |  |

|------|------|----------------|--|--|--|--|--|--|--|

| DRS1 | DRS0 | Drive Strength |  |  |  |  |  |  |  |

| 0    | 0    | 100%           |  |  |  |  |  |  |  |

| 0    | 1    | 75%            |  |  |  |  |  |  |  |

| 1    | 0    | 50%            |  |  |  |  |  |  |  |

| 1    | 1    | 25%            |  |  |  |  |  |  |  |

## 7.5. READ Operations

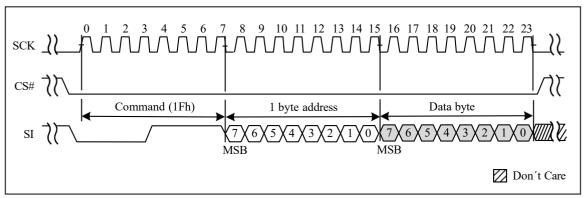

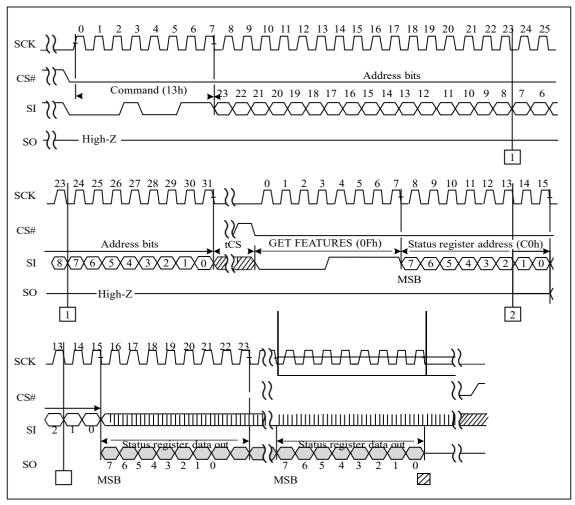

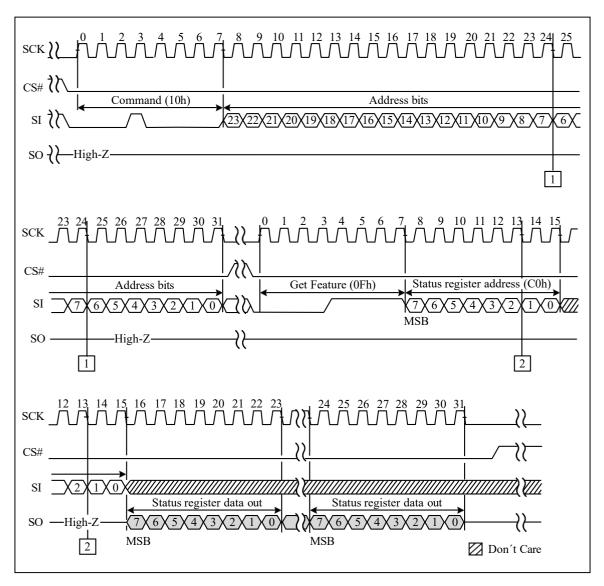

## 7.5.1. PAGE READ (13h)

The PAGE READ (13h) command transfers the data from the NAND Flash array to the cache register. The command sequence to transfer data from array to output is as follows:

- 13h (PAGE READ to cache register)

- 0Fh (GET FEATURE command to read the status)

- 03h or 0Bh (Read from Cache x1); or 3Bh (Read From Cache x2); or 6Bh (Read from Cache x4)

The PAGE READ command requires a 24-bit address consisting of 8 dummy bits followed by a 16-bit block/page address. After the block/page addresses are registered, the device starts the transfer from the main array to the cache register, and is busy for tRD time. During this time, the GET FEATURE (0Fh) command can be issued to monitor the status of the operation. Following a status of successful completion, the READ FROM CACHE command must be issued in order to read the data out of the cache. The READ FROM CACHE command requires 4 dummy bits, followed by a 12-bit column address for the

Starting byte address. The starting byte address can be 0 to 2176, but after the end of the cache register is reached, the data does not wrap around and SO goes to a High-Z state.

Figure 12: PAGE READ (13h) Timing

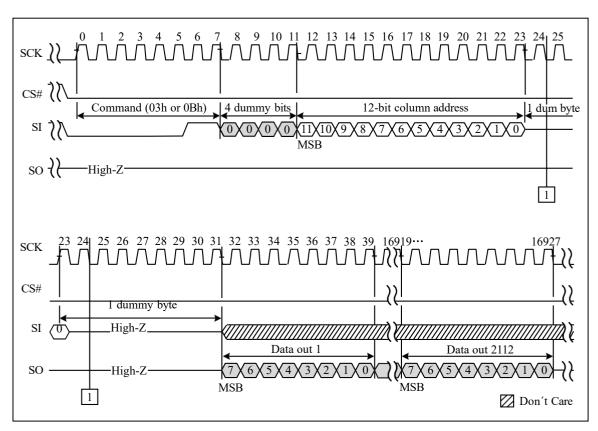

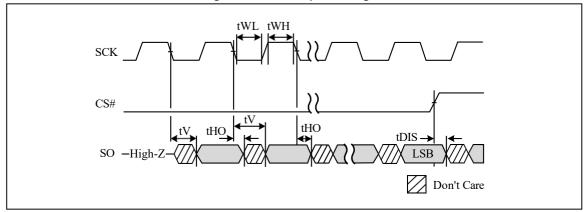

## 7.5.2. READ FROM CACHE x1 (03h or 0Bh)

The READ FROM CACHE x1 command allows one or more data bytes to be sequentially read from the cache buffer after executing this command. This command is initiated by driving the CS# pin low and then shifting the command op code (03h/0Bh) followed by the 16 bit column address and 8-bit dummy clocks. After the address is received, the data byte of the addressed cache buffer location will be shifted out on the SO pin at the falling edge of SCK with most significant bit (MSB) first. The address is automatically incremented to the next higher address after each byte of data is shifted out allowing for a continuous stream of data. This command is completed by driving CS# high.

Figure 13: READ FROM CACHE x1 (03h or 0Bh) Timing

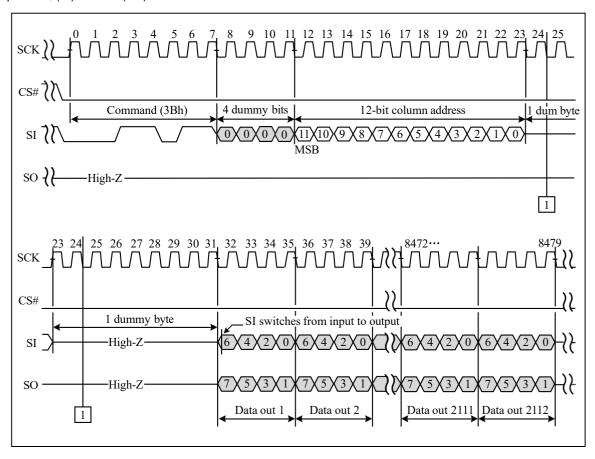

## 7.5.3. READ FROM CACHE x2 (3Bh)

The READ FROM CACHE x2 (3Bh) command is similar to Read from Cache (03h or 0Bh) except that data is output on two pins: IO<sub>0</sub> (SI) and IO<sub>1</sub> (SO). This allows data to be transferred at twice the rate of 03h/0Bh command.

Figure 14: READ FROM CACHE x2 (3Bh) Timing

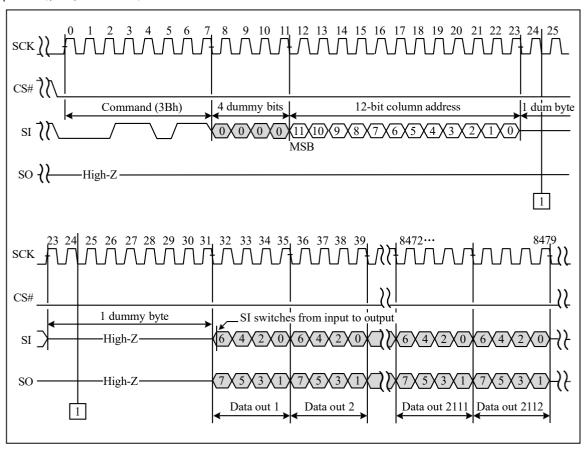

## 7.5.4. READ FROM CACHE x4 (6Bh)

The READ FROM CACHE x4 (6Bh) command is similar to Read from Cache (03h or 0Bh) except that data is output on four pins: IO<sub>0</sub>, IO<sub>1</sub>, IO<sub>2</sub> and IO<sub>3</sub>. This allows data to be transferred at four times the rate of 03h/0Bh command.

Figure 15: READ FROM CACHE x4 (6Bh) Timing

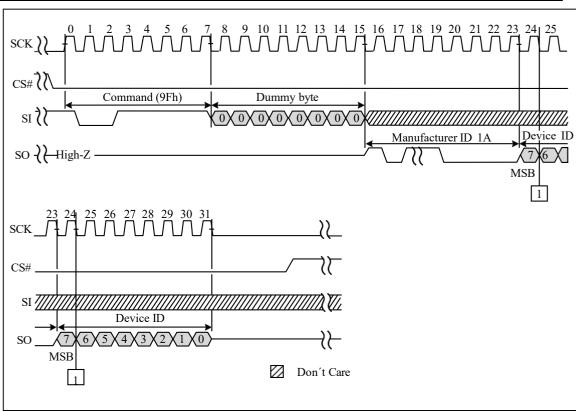

## 7.5.5. READ ID (9Fh)

The READ ID command is used to read the 2 bytes of identifier code programmed into the NAND Flash device. The READ ID command reads a 2-byte table (see below) that includes the Manufacturer ID and the device configuration.

| Tab | le 7: | RFA | D ID | ) Table |

|-----|-------|-----|------|---------|

|     |       |     |      |         |

| Byte | Description            | 107 | 106 | 105 | 104 | IO3 | IO2 | IO1 | 100 | Value |

|------|------------------------|-----|-----|-----|-----|-----|-----|-----|-----|-------|

| 0    | Manufacture ID (t.b.d) | 0   | 0   | 0   | 1   | 1   | 0   | 1   | 0   | 1Ah   |

| 1    | Device ID (2Gb, 3.3V)  | 0   | 0   | 1   | 0   | 0   | 1   | 0   | 0   | 24h   |

Figure 16: READ ID (9Fh) Timing

## 7.5.6. Parameter Page

The following command flow must be issued by the memory controller to access the parameter page contained within UniIC SPI devices:

- SET FEATURE (1Fh) command with feature address B0h and data value of 40h (Access to OTP/Parameter/UniqueID pages, ECC disable).

- PAGE READ (13h) command with block/page address of 0x01h, and then check the status of the read completion using the GET FEATURE (0Fh) command with feature address C0h.

- READ FROM CACHE (03h) command with an address of 0x00h to read the data out of the NAND device (refer to the following Parameter Page Data Structure table for a description of the contents of the parameter page).

- To exit reading the parameter page, issue SET FEATURE (1Fh) command with feature address B0h and data value of 10h or 00h (main array READ, ECC enable/disable).

| Table 8: Parameter Page Data Structure |                                                                                                                                                                                                                                                                        |                                                                                         |  |  |  |  |  |

|----------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|--|--|--|--|--|

| Byte                                   | Description                                                                                                                                                                                                                                                            | Value <sup>1</sup>                                                                      |  |  |  |  |  |

| 0-3                                    | Parameter Page Signature                                                                                                                                                                                                                                               | 4Fh (O), 4Eh (N), 46h (F), 49h (I)                                                      |  |  |  |  |  |

| 4-5                                    | Revision number                                                                                                                                                                                                                                                        | 00h, 00h                                                                                |  |  |  |  |  |

| 6-7                                    | Feature Supported                                                                                                                                                                                                                                                      | 00h, 00h                                                                                |  |  |  |  |  |

| 8-9                                    | Optional Commands Supported 15-6: Reserved (0) 5: 1 = supports Read UniqueID 4: 1 = supports Copy back 3: 1 = supports Read Status Enhanced 2: 1 = supports Get Feature and Set Feature 1: 1 = supports Read Cache commands 0: 1 = supports Page Cache Program command | 24h, 00h                                                                                |  |  |  |  |  |

| 10-31                                  | Reserved                                                                                                                                                                                                                                                               | 00h, 00h, 00h, 00h, 00h, 00h, 00h, 00h,                                                 |  |  |  |  |  |

| 32-43                                  | Device Manufacturer                                                                                                                                                                                                                                                    | 55h, 4Eh, 49h, 49h, 43h, 20h, 20h, 20h, 20h, 20h, 20h, 20h, 20                          |  |  |  |  |  |

| 44-63                                  | Device Model                                                                                                                                                                                                                                                           | 53h, 43h, 46h, 32h, 42h, 57h, 31h, 49h, 33h, 41h, 20h, 20h, 20h, 20h, 20h, 20h, 20h, 20 |  |  |  |  |  |

| 64                                     | Manufacture ID                                                                                                                                                                                                                                                         | 1Ah                                                                                     |  |  |  |  |  |

| 65-66                                  | Date code                                                                                                                                                                                                                                                              | 00h, 00h                                                                                |  |  |  |  |  |

| 67-79                                  | Reserved                                                                                                                                                                                                                                                               | 00h, 00h, 00h, 00h, 00h, 00h, 00h, 00h,                                                 |  |  |  |  |  |

| 80-83                                  | Number of data bytes per page 00h, 08h, 00h, 00h                                                                                                                                                                                                                       |                                                                                         |  |  |  |  |  |

| 84-85                                  | Number of spare bytes per page                                                                                                                                                                                                                                         | 80h, 00h (ECC Off)                                                                      |  |  |  |  |  |

| 86-89                                  | Number of data bytes per partial page                                                                                                                                                                                                                                  | 00h, 02h, 00h, 00h                                                                      |  |  |  |  |  |

| 90-91                                  | Number of spare bytes per partial page                                                                                                                                                                                                                                 | 20h, 00h (ECC Off)                                                                      |  |  |  |  |  |

| 92-95                                  | Number of pages per block                                                                                                                                                                                                                                              | 40h, 00h, 00h, 00h                                                                      |  |  |  |  |  |

| 96-99                                  | Number of blocks per unit                                                                                                                                                                                                                                              | 00h, 08h, 00h, 00h                                                                      |  |  |  |  |  |

| 100                                    | Number of logical units                                                                                                                                                                                                                                                | 01h                                                                                     |  |  |  |  |  |

| 101                                    | Number of address cycles                                                                                                                                                                                                                                               | 00h                                                                                     |  |  |  |  |  |

| 102                                    | Number of bits per cell                                                                                                                                                                                                                                                | 01h                                                                                     |  |  |  |  |  |

| 103-104                                | Bad blocks maximum per unit                                                                                                                                                                                                                                            | 29h, 00h (2Gb)                                                                          |  |  |  |  |  |

| Byte    | Description                                    | Value <sup>1</sup>                                                                                                                      |  |  |

|---------|------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 105-106 | Block endurance                                | 0Ah, 04h (Byte 105 comprised the value; byte 106 comprised the multiplier; the calculation equation is value x 10 <sup>multiplier</sup> |  |  |

| 107     | Guaranteed valid blocks at beginning of target | 04h                                                                                                                                     |  |  |

| 108-109 | Block endurance for guaranteed valid blocks    | 00h, 00h                                                                                                                                |  |  |

| 110     | Number of programs per page                    | 04h                                                                                                                                     |  |  |

| 111     | Partial programming attributes                 | 00h                                                                                                                                     |  |  |

| 112     | Number of ECC bits                             | 00h                                                                                                                                     |  |  |

| 113     | Number of interleaved address bits             | 00h                                                                                                                                     |  |  |

| 114     | Interleaved operation attributes               | 00h                                                                                                                                     |  |  |

| 115-127 | Reserved                                       | 00h, 00h, 00h, 00h, 00h, 00h, 00h, 00h,                                                                                                 |  |  |

| 128     | I/O Pin Capacitance                            | 0Ah (pf)                                                                                                                                |  |  |

| 129-130 | Timing mode Support                            | 00h, 00h (n/a)                                                                                                                          |  |  |

| 131-132 | Program Cache timing                           | 00h, 00h (n/a)                                                                                                                          |  |  |

| 133-134 | tPROG maximum page program time                | 58h, 02h (600us)                                                                                                                        |  |  |

| 135-136 | tBERS maximum block erase time                 | 10h, 27h (10000us)                                                                                                                      |  |  |

| 137-138 | tR maximum page read time                      | 19h, 00h (25us)                                                                                                                         |  |  |

| 139-163 | Reserved                                       | 00h, 00h, 00h, 00h, 00h, 00h, 00h, 00h,                                                                                                 |  |  |

| 164-165 | Vendor-specific revision number                | 00h, 00h (n/a)                                                                                                                          |  |  |

| 166-253 | Vendor specific                                | 00h, 00h, 00h, 00h, 00h, 00h, 00h, 00h,                                                                                                 |  |  |

| 254-255 | Integrity CRC                                  | FFh, 72h                                                                                                                                |  |  |

| 256-511 | Value of bytes 0-255                           |                                                                                                                                         |  |  |

| 511-767 | Value of bytes 0-255                           |                                                                                                                                         |  |  |

| 768+    | Additional redundant parameter pages           |                                                                                                                                         |  |  |

**Note:** 1. h = hexadecimal.

## 7.5.7. UniqueID Page

The following command flow must be issued by the memory controller to access the uniqueID page contained within UnIIC SPI devices:

- SET FEATURE (1Fh) command with feature address B0h and data value of 40h (Access to OTP/Parameter/UniqueID pages, ECC disable).

- PAGE READ (13h) command with block/page address of 0x00h, and then check the status of the read completion using the GET FEATURE (0Fh) command with feature address C0h.

- READ FROM CACHE (03h) command with an address of 0x00h to read the data out of the NAND device. (The contents of the UniqueID page are described in the following note.)

**Note:** The device stores 16 copies of the unique ID data. Each copy is 32 bytes; the first 16 bytes are unique data, and the second 16 bytes are the complement of the first 16 bytes. The host should XOR the first 16 bytes with the second 16 bytes. If the result is 16 bytes of FFh, then that copy of the unique ID data is correct. If a non-FFh result is returned, the host can repeat the XOR operation on a subsequent copy of the unique ID data

• To exit reading the UniqueID page, issue SET FEATURE (1Fh) command with feature address B0h and data value of 10h or 00h (main array READ, ECC enable/disable).

## 7.6. Program Operations

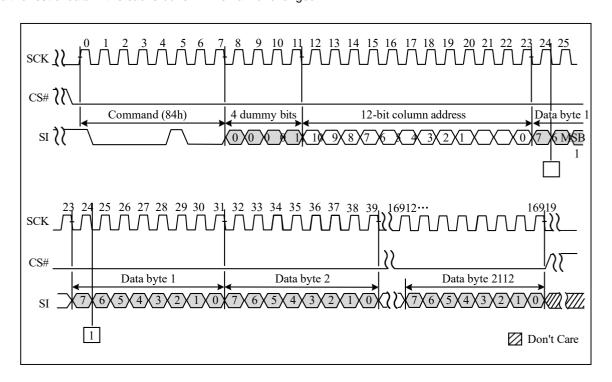

#### 7.6.1. PAGE PROGRAM

The PAGE PROGRAM operation sequence programs 1 byte to 2,176 or 2,112 bytes of data within a page. The page program sequence is as follows:

- 06h (WRITE ENABLE)

- 02h (PROGRAM LOAD)

- 10h (PROGRAM EXECUTE)

- 0Fh (GET FEATURE command to read the status)

Prior to performing the PROGRAM LOAD operation, a WRITE ENABLE (06h) command must be issued. As with any command that changes the memory contents, the WRITE ENABLE must be executed in order to set the WEL bit. If this command is not issued, then the rest of the program sequence is ignored. WRITE ENABLE must be followed by a PROGRAM LOAD (02h) command. PROGRAM LOAD consists of an 8-bit Op code, followed by 4 dummy bits, followed by a 12-bit column address, then the data bytes to be programmed. The data bytes are loaded into a cache register that is 2176 or 2112 bytes long. Only four partial- page programs are allowed on a single page. If more than 2176 or 2112 bytes are loaded, then those additional bytes are ignored by the cache register. The command sequence ends when CS# goes from LOW to HIGH.

After the data is loaded, a PROGRAM EXECUTE (10h) command must be issued to initiate the transfer of data from the cache register to the main array. PROGRAM EXECUTE consists of an 8-bit Op code, followed by a 24-bit address (7 dummy bits and a 17-bit page/block address for 2Gb). After the page/block address is registered, the memory device starts the transfer from the cache register to the main array, and is busy for tPROG time. During this busy time, the status register can be polled to monitor the status of the operation. When the operation completes successfully, the next series of data can be loaded with the PROGRAM LOAD command.

Figure 17: PROGRAM LOAD (02h) Timing

Figure 18: PROGRAM EXECUTE (10h) Timing

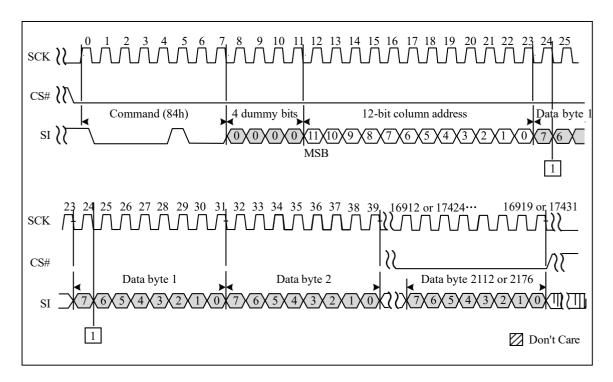

#### 7.6.2. RANDOM DATA PROGRAM

The RANDOM DATA PROGRAM sequence programs or replaces data in a page with existing data. The random data program sequence is as follows:

- 06h (WRITE ENABLE)

- 84h (PROGRAM LOAD RANDOM DATA)

- 10h (PROGRAM EXECUTE)

- 0Fh (GET FEATURE command to read the status)

Prior to performing a PROGRAM LOAD RANDOM DATA operation, a WRITE ENABLE (06h) command must be issued to change the contents of the memory array. Following a WRITE ENABLE (06) command, a PROGRAM LOAD RANDOM DATA (84h) command must be issued. This command consists of an 8-bit Op code, followed by 4 dummy bits, followed by a 12-bit column address. New data is loaded in the column address provided with the 12 bits. If the random data is not sequential, then another PROGRAM LOAD RANDOM DATA (84h) command must be issued with a new column address. After the data is loaded, a PROGRAM EXECUTE (10h) command can be issued to start the programming operation.

Both PROGRAM LOAD x1 and PROGRAM LOAD RANDOM DATA x1 instructions are the same command sequence. The difference is that PROGRAM LOAD x1 instruction will reset the cache buffer to all FFh value, while PROGRAM LOAD RANDOM DATA x1 instruction will only update the data bytes that are specified by the command input sequence and the rest of data in the cache buffer will remain unchanged.

Figure 19: PROGRAM LOAD RANDOM DATA (84h) Timing

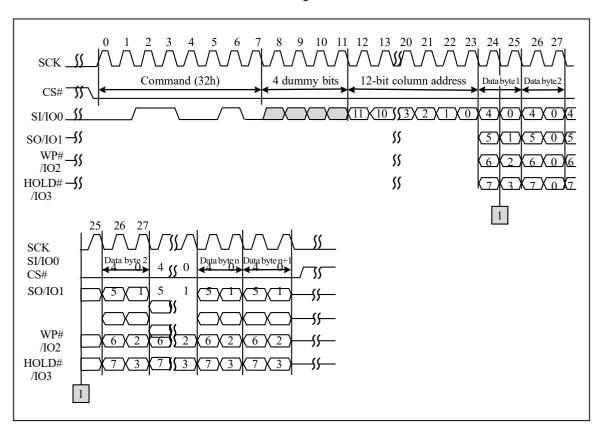

# 7.6.3. PROGRAM LOAD x4 (32h) / PROGRAM LOAD RANDOM DATA x4 (34h)

The PROGRAM LOAD x4 and PROGRAM LOAD RANDOM DATA x4 instructions are enigmatical to the PROGRAM LOAD and PROGRAM LOAD RANDOM DATA in terms of operation sequence and functionality. The only difference is that x4 instructions will input the data bytes from all four IO pins instead of the single SI pin. This method will significantly shorten the data input time when a large amount of data needs to be loaded into the cache buffer.

Both PROGRAM LOAD x4 and PROGRAM LOAD RANDOM DATA x4 instructions are the same command sequence. The difference is that PROGRAM LOAD x4 instruction will reset the cache buffer to all FFh value, while PROGRAM LOAD RANDOM DATA x4 instruction will only update the data bytes that are specified by the command input sequence and the rest of data in the cache buffer will remain unchanged.

Figure 20: PROGRAM LOAD x4 (32h) Timing

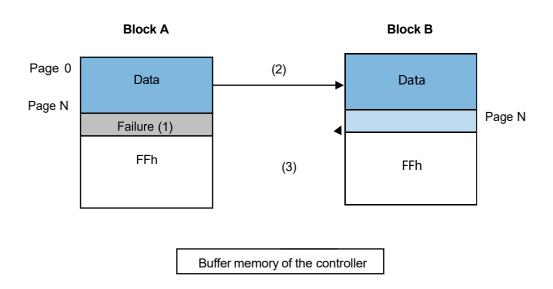

#### 7.6.4. INTERNAL DATA MOVE

The INTERNAL DATA MOVE command sequence programs or replaces data in a page with existing data. The INTERNAL DATA MOVE command sequence is as follows:

- 13h (PAGE READ to cache register)

- 06h (WRITE ENABLE)

- 84h (PROGRAM LOAD RANDOM DATA) or 34h (PROGRAM LOAD RANDOM DATA x4)

- 10h (PROGRAM EXECUTE)

- 0Fh (GET FEATURE command to read the status)

Prior to performing an internal data move operation, the target page content must be read into the cache register. This is done by issuing a PAGE READ (13h) command. The

PAGE READ command must be followed with a WRITE ENABLE (06h) command in order

to change the contents of memory array. After the WRITE ENABLE command is issued, the PROGRAM LOAD RANDOM DATA (84h) command or PROGRAM LOAD RANDOM

DATA x4 (34h) can be issued. This command consists of an 8-bit Op code, followed by 4 dummy bits, followed by a 12-bit column address. New data is loaded in the 12-bit column address. If the random data is not sequential, another PROGRAM LOAD RANDOM DATA (84h) command or PROGRAM LOAD RANDOM DATA x4 (34h) must be issued with the new column address. After the data is loaded, a PROGRAM EXECUTE (10h) command can be issued to start the programming operation. It is not possible to use the INTERNAL DATA MOVE operation to move data from one die (LUN) to another.

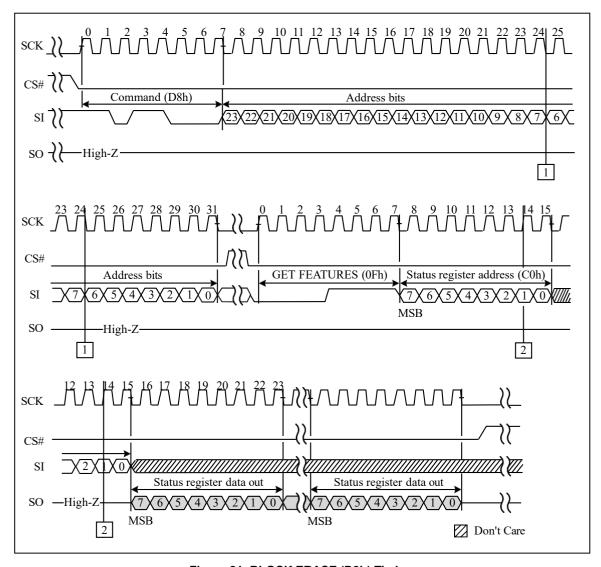

## 7.7. BLOCK ERASE (D8h)

The BLOCK ERASE (D8h) command is used to erase at the block level. The blocks are organized as 64 pages per block, 2176 bytes per page (2048 + 128 bytes). Each block is 136 Kbytes. The BLOCK ERASE command (D8h) operates on one block at a time. The command sequence for the BLOCK ERASE operation is as follows:

- 06h (WRITE ENABLE)

- D8h (BLOCK ERASE)

- 0Fh (GET FEATURE command to read the status)

Prior to performing the BLOCK ERASE operation, a WRITE ENABLE (06h) command must be issued. As with any command that changes the memory contents, the WRITE ENABLE command must be executed in order to set the WEL bit. If the WRITE ENABLE command is not issued, then the rest of the erase sequence is ignored. A WRITE ENABLE command must be followed by a BLOCK ERASE (D8h) command. This command requires a 24-bit address consisting of 7 dummy bits followed by a 17-bit page/block address for 2Gb. After the row address is registered, the control logic automatically controls timing and erase-verify operations. The device is busy for tERS time during the BLOCK ERASE operation. The GET FEATURE (0Fh) command can be used to monitor the status of the operation.

Figure 21: BLOCK ERASE (D8h) Timing

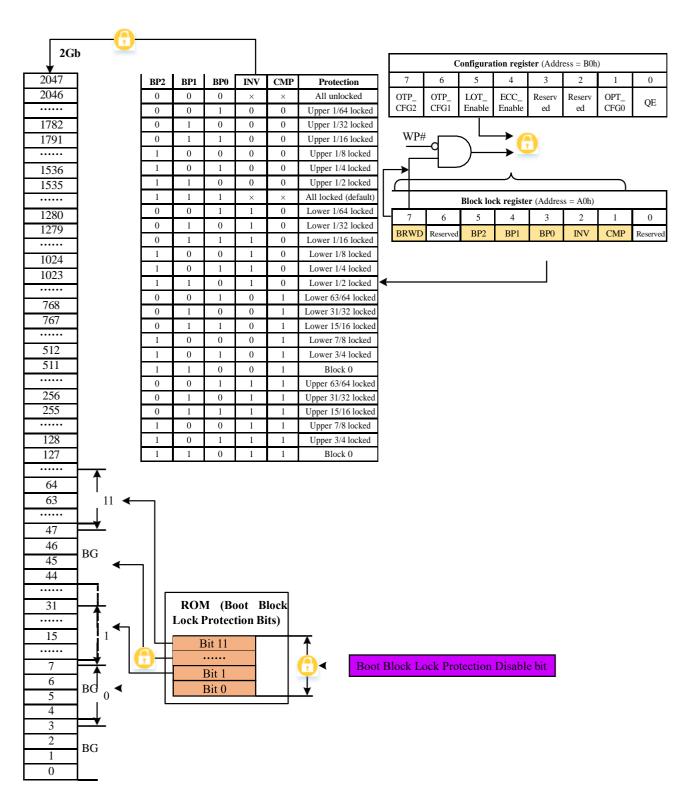

#### 7.8. Block Lock Feature

The block lock feature protects either the entire device or ranges of blocks from being programmed or erased.

Before the contents of the device can be modified, the device must first be unlocked. Either a range of blocks or the entire device may be unlocked. PROGRAM and ERASE operations complete successfully only in the block ranges that have been unlocked. Blocks, once unlocked, can be locked again to protect them from further PROGRAM and Erase operations.

Also blocks that are locked can be protected further or locked tight. When locked tight, the device's blocks can no longer be locked or unlocked unless next power cycle.

But once the blocks are locked through Protect command, these blocks would be permanently protected from PROGRAM or ERASE operations.

The following diagram shows block lock scheme in this product.

Figure 23: Block Lock Scheme

#### 7.8.1. Block Lock

The block lock feature provides the ability to protect the entire device, or ranges of blocks, from the PROGRAM and ERASE operations. After power-up, the device is in the locked state, i.e., bits 1, 2, 3, 4, and 5 of the block lock register are set to 1. To unlock all the blocks, or lock a range of blocks, the SET FEATURE command must be issued with feature address A0h and data value of the block protection bits shown in Table 9. When BRWD is set and WP# is LOW, none of the writable bits (1, 2, 3, 4, 5 and 7) in the block lock register can be changed. Also, when a PROGRAM/ERASE command is issued to a locked block, a status to indicate operation failure is returned. When an ERASE command is issued to a locked block, the erase failure, 04h, is returned. When a PROGRAM command is issued to a locked block, program failure, 08h, is returned.

**Table 9: Block Lock Register Block Protection Bits**

| Block Protection Bits |     |     |     |     | Protected Portion    |

|-----------------------|-----|-----|-----|-----|----------------------|

| BP2                   | BP1 | BP0 | INV | СМР | Trotootod Fortion    |

| 0                     | 0   | 0   | Х   | Х   | All unlocked         |

| 0                     | 0   | 1   | 0   | 0   | Upper 1/64 locked    |

| 0                     | 1   | 0   | 0   | 0   | Upper 1/32 locked    |

| 0                     | 1   | 1   | 0   | 0   | Upper 1/16 locked    |

| 1                     | 0   | 0   | 0   | 0   | Upper 1/8 locked     |

| 1                     | 0   | 1   | 0   | 0   | Upper 1/4 locked     |

| 1                     | 1   | 0   | 0   | 0   | Upper 1/2 locked     |

| 1                     | 1   | 1   | Х   | Х   | All locked (default) |

| 0                     | 0   | 1   | 1   | 0   | Lower 1/64 locked    |

| 0                     | 1   | 0   | 1   | 0   | Lower 1/32 locked    |

| 0                     | 1   | 1   | 1   | 0   | Lower 1/16 locked    |

| 1                     | 0   | 0   | 1   | 0   | Lower 1/8 locked     |

| 1                     | 0   | 1   | 1   | 0   | Lower 1/4 locked     |

| 1                     | 1   | 0   | 1   | 0   | Lower 1/2 locked     |

| 0                     | 0   | 1   | 0   | 1   | Lower 63/64 locked   |

| 0                     | 1   | 0   | 0   | 1   | Lower 31/32 locked   |

| 0                     | 1   | 1   | 0   | 1   | Lower 15/16 locked   |

| 1                     | 0   | 0   | 0   | 1   | Lower 7/8 locked     |

| 1                     | 0   | 1   | 0   | 1   | Lower 3/4 locked     |

| 1                     | 1   | 0   | 0   | 1   | Block 0              |

| 0                     | 0   | 1   | 1   | 1   | Upper 63/64 locked   |

| 0                     | 1   | 0   | 1   | 1   | Upper 31/32 locked   |

| 0                     | 1   | 1   | 1   | 1   | Upper 15/16 locked   |

| 1                     | 0   | 0   | 1   | 1   | Upper 7/8 locked     |

| 1                     | 0   | 1   | 1   | 1   | Upper 3/4 locked     |

| 1                     | 1   | 0   | 1   | 1   | Block 0              |

For example, if all the blocks need to be unlocked after device initialization, the following sequence should be performed:

- Issue SET FEATURE command (1Fh)

- Issue the feature address to unlock the block (A0h)

- · Issue 00h on data bits to unlock all blocks

#### 7.8.2. LOCK TIGHT

Lock Tight prevents locked blocks from being unlocked and also prevents unlocked blocks from being locked. Once Lock Tight is enabled, this mode cannot be disabled via a software command and BP bits, INV and CMP bit and BRWD is protected from further software change. Only another power down and power up cycle could disable Lock Tight. The command sequence to enable LOCK TIGHT is as follows:

- Issue SET FEATURE command (1h)

- Issue the feature address to configuration register bits (B0h)

- · Issue 20h on data bits to enable lock tight

During Quad mode, this could provide software protection to prevent locked/unlocked blocks from change if WP# is disabled.

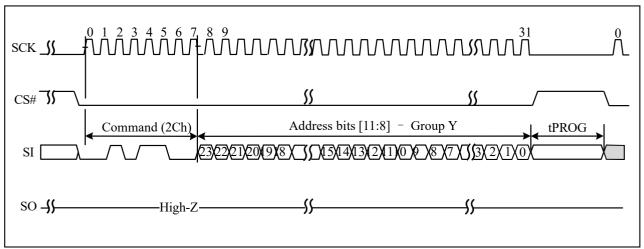

# 7.8.3. PROTECT Command (PERMANENT BLOCK LOCK PROTECTION 2Ch)

The PROTECT command provides nonvolatile, irreversible protection of up to twelve groups (48 blocks total, also named as boot blocks) shown in Figure 22, "Block Lock Scheme (2Gb)" on page 36.

Implementation of the protection is group-based, which means that a minimum of one group (4 blocks) is protected when the PROTECT command is issued. Because block protection is nonvolatile, a power-on or power-off sequence does not affect the block status after the PROTECT command is issued. The device ships from the factory with no blocks protected so that users can program or erase the blocks before issuing the PROTECT command. Block protection is also irreversible in that when protection is enabled by the issuing PROTECT command, the protected blocks can no longer be programmed or erased. If Boot block lock protection disable mode is enabled, PROTECT command would be ignored and has no busy time.

The PROTECT sequence is as detailed below:

- 06h (WRITE ENABLE)

- 2Ch (Permanent Block Lock Protection)

- 0Fh (GET FEATURE command to read the status)

Prior to performing the Protection command (2Ch), a WRITE ENABLE (06h) command must be issued. As with any command that changes the memory contents, the WRITE ENABLE must be executed in order to set the WEL bit. If this command is not issued, then the protection command is ignored. WRITE ENABLE must be followed by a Protection command (2Ch). The Protection command consists of an 8-bit Op code, followed by a 24- bit address (7 dummy bits and a 17-bit page/block address for 2Gb).

After the page/block address is registered, the corresponding boot block lock protection bit would be programmed to lock corresponding boot block group. This operation is shown in Figure 22, "Protection Command (2Ch) Timing" on page 40. During this busy time, the status register can be polled to monitor the status of the operation.  $P_FAIL$  bit = 0 indicates the success of protection operation;  $P_FAIL$  bit = 1 indicates the failure of protection operation.

Figure 24: Protection Command (2Ch) Timing

### 7.8.3.1. PROTECTION Command Details

To enable protection, the Protection command consists of an 8-bit Op code, followed by a 24-bit address (7 dummy bits and a 17-bit page/block address for 2Gb). Row address bits 8, 9, 10, 11 (named as Y, bit 12~15 must be kept as '0') input the targeted block group information.

This Y defines the group of blocks to be protected. There are always 12 Groups, so Y = 0000b - 1011b:

- Y = 0000 protects Group0 = blks 0, 1, 2, 3

- Y = 0001 protects Group1 = blks 4, 5, 6, 7

- Y = .....

- Y = 1011 protects Group11 = blks 44, 45, 46, 47

After tPROG, the targeted block groups are protected. Upon PROTECT operation failure, the status register reports a value of 08h (P\_FAIL = 1). Upon PROTECT operation success, the status register reports value of 00h.

### 7.9. OTP Feature

The serial device offers a protected, one-time programmable (OTP) NAND Flash memory area. Ten full pages (2176 or 2112 bytes per page) are available on the device, and the entire range is guaranteed to be good.

Customers can use the OTP area any way they want; typical uses include programming serial numbers, or other data, for permanent storage.

The OTP area leaves the factory in an erased state (all bits are 1). Programming an OTP page changes bits that are 1 to 0, but cannot change bits that are 0 to 1. The OTP area cannot be erased, even if it is not protected. Protecting the OTP area prevents further programming of the pages in the OTP area.

To access the OTP feature, the user must issue the SET FEATURE command, followed by feature address B0h. When the OTP is ready for access, pages 02h-0Bh can be programmed in sequential order. The PROGRAM LOAD (02h) and PROGRAM EXECUTE (10h) commands can be used to program the pages. Also, the PAGE READ (13h) command can be used to read the OTP area. The data bits used in feature address B0h to enable OTP access are shown in the Table 10, "OTP Configuration States" on page 41.

### 7.9.1. OTP Access Configuration

To access OTP, perform the following command sequence:

- Issue the SET FEATURE command (1Fh)

- Issue the configuration feature address (B0h)

- Issue the PAGE PROGRAM or PAGE READ command

For OTP states, see the following table.

**Table 10: OTP Configuration States**

| OTP_CFG2 | OTP_CFG1 | OTP_CFG0 | State                                                                                           |

|----------|----------|----------|-------------------------------------------------------------------------------------------------|

| 0        | 0        | 0        | Normal Operation                                                                                |

| 0        | 1        | 0        | Access OTP area / Parameter page / UniqueID (named as OTP Operation Mode)                       |

| 1        | 0        | 0        | Normal Operation (Reserved)                                                                     |

| 1        | 1        | 0        | Access to OTP Data Protection bit to lock OTP area (named as OTP DATA protection mode)          |

| 0        | 0        | 1        | Normal Operation (Reserved)                                                                     |

| 0        | 1        | 1        | Normal Operation (Reserved)                                                                     |

| 1        | 0        | 1        | Normal Operation (Reserved)                                                                     |

| 1        | 1        | 1        | Access to Disable Boot Block Lock Protection (named as Boot block lock protection disable mode) |

### 7.9.2. OTP Area Access

The OTP area is accessible while the OTP operation mode is enabled. To enable OTP operation mode, issue the SET FEATURE (1Fh) command to feature address B0h and data value of 40h (OTP operation mode and ECC disable) or 50h (OTP operation mode and ECC enable).

When the die is in OTP operation mode, all subsequent PAGE PROGRAM or PAGE READ commands are applied to the OTP area. Erase commands are not valid while the device is in OTP operation mode.

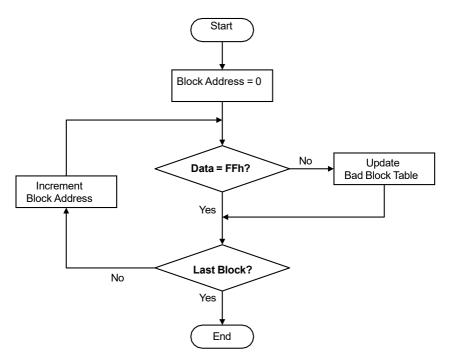

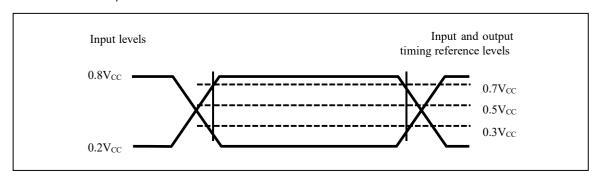

Each page in the OTP area is programming using the PAGE PROGRAM sequence described at Section 8.6.1, "PAGE PROGRAM". Each page can be programmed more than once up to the maximum number allowed. By reading the P\_FAIL bit of the status register, program operation passed or failed could be determined. If the host attempts to program the OTP pages which are out of bounds, program command will be ignored and P\_FAIL bit = 1 will be reported. If the host attempts to program the OTP pages after OTP area is protected, the program command will be ignored and P\_FAIL bit is set to '1' indicating program failure.