西安紫光国芯半导体有限公司数字后端设计团队,目标为客户提供完整的从RTL代码之后到GDS数据流片的全流程服务,同时也可以为客户在后端实现具体领域提供专业技术服务和解决方案。

团队设计服务工作起始于2010年,在过去十年多时间为客户成功完成了超过40个芯片的物理设计工作。团队成员中硕士学历占比80%;成员技术能力覆盖综合,PR,时序收敛,物理收敛,功耗分析,可靠性分析全流程;核心工程师工作经经验超过7年,最长工作经验超过15年;独立负责过芯片顶层和单独流片的工程师超过25%;

服务内容

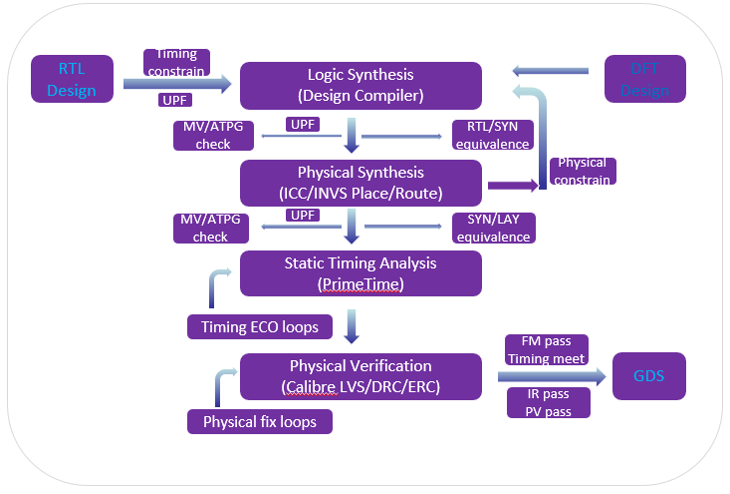

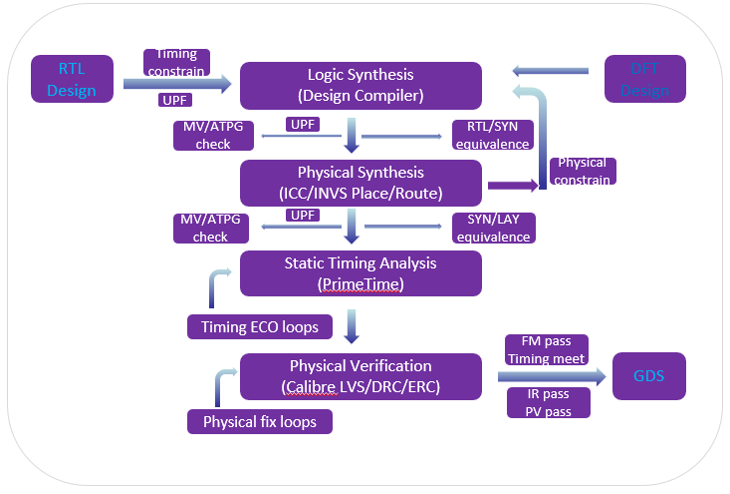

数字后端设计服务主要工作为从RTL之后开始,到GDS数据流片至foundry生产制造。

数字后端设计团队提供以下设计服务和技术顾问

• 负责从RTL完成到满足signoff标准的GDS输出一站式全芯片设计服务工作;

• 也可以负责RTL2GDS过程中任一阶段的设计工作,包含但不限于:

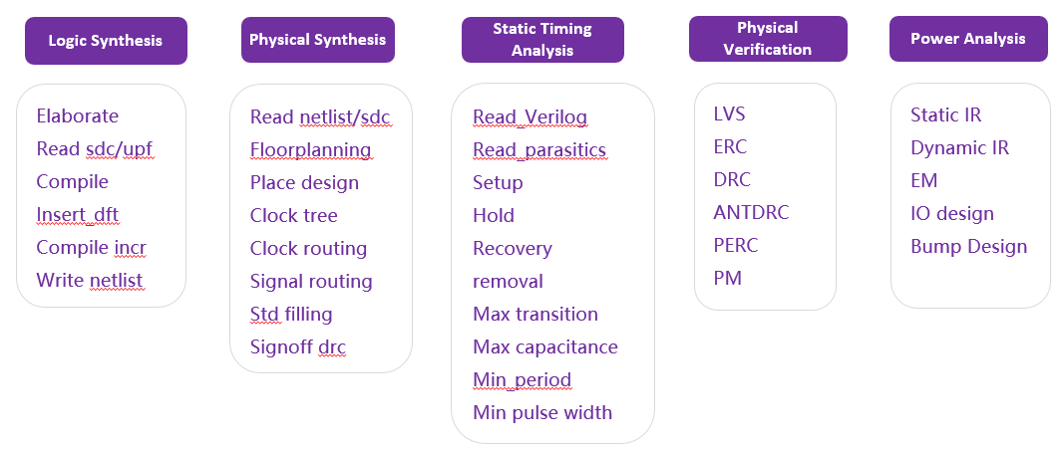

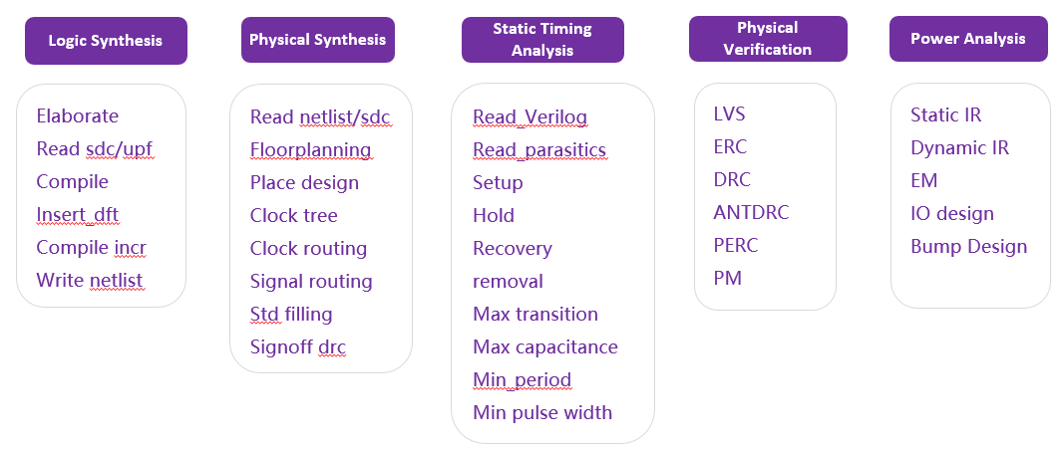

• 基于客户RTL和设计意图描述,编写规范的时序约束;

• 完成满足一定时序和面积指标的从RTL到门级网表的综合工作,即逻辑综合;

• 完成在后端设计各阶段的逻辑等价性验证;

• 完成基于不同工艺节点下一定面积和功耗要求的PR工作,即物理综合;

• 完成全芯片的静态时序分析和signoff,包含信号完整性分析;

• 完成全芯片的物理验证和signoff,包含DFM验证;

• 完成全芯片各种模式下功耗定量分析和功耗最优化实现;

• 完成芯片的电源完整性分析,包含仅芯片的和带封装结构的IR、EM分析;

• 在芯片上完成封装相关的工作,与封装厂完成协同设计;

• 流片(Tape Out)之后到开始制造前的JDV检查确认;

• 回片(Wafer Out)之后跟bumping厂以及封装厂的协同支持;

我们的能力

设计能力覆盖

• 参与超过40个芯片的后端设计和流片;

• 完成工艺节点65nm,55nm,40nm下的全芯片后端实现;

• 高性能模块(CPU,GPU,VPU,DSP)的后端设计实现;

• 基于UPF的低功耗芯片的后端设计实现;

• 高速IP集成(Serdes,PCIE, DDR,MIPI)的后端设计实现;

• 超大规模和超大面积芯片(800 mm2)的后端收敛;

后端设计项目

• 多款手机基带芯片,TSMC40nm/TSMC28nm/Intel 14nm,完整持续的基于UPF的多电压域设计后端收敛

• 多款手机基带芯片,TSMC28nm/Intel 14nm,modem模块3G子系统和4G子系统的后端实现

• 网络交换芯片,TSMC 7nm,1.2GHz,100 Million单元子系统后端设计

• 多款手机基带芯片,TSMC28nm,Mali系列GPU后端设计

• 手机基带芯片,Intel14nm,Synopsys CPU后端设计

全芯片后端设计

• 桥接芯片,GF12nm,芯片面积20 mm2,集成GDDR6 IP,全芯片后端设计

• 网络交换芯片,SMIC40nm,230+ mm2;集成PCIE IP,集成SEDES IP,全芯片后端设计

• 高带宽芯片,55nm,芯片面积800mm2,全芯片后端设计

• 视频芯片,Samsung 14nm,芯片面积50mm2,集成MIPI IP,集成DSI/CSI IP,全芯片后端设计

• 网络转换芯片,SMIC65nm,芯片面积50mm2,集成SEDES IP,集成GPHY IP,全芯片后端设计

开发流程

合作模式

依据过去项目的成功经验,西安紫光国芯提供灵活的商业合作模式来满足不同客户和客户项目不同阶段的需求。

工作内容方式

• 完整的全芯片TurnKey模式,客户完成RTL设计或者提供门级网表,后端提供到GDS流片一站式设计服务;

• 在客户项目中,单独负责后端某一领域工作的交付和签核;

• 在客户项目中,负责一些模块或者子系统的全流程设计,协同完成后端设计;

• 提供专业人员为客户某一具体问题提供专业技术服务和解决方案;

工作环境方式

• 客户交付逻辑综合结果,在西安紫光国芯环境中完成网表到GDS的工作交付给客户;

• 建立独立的离岸设计中心(ODC)远程接入客户项目环境工作;